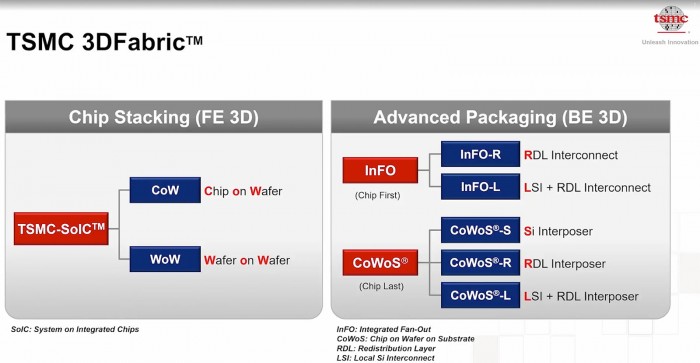

在官方 M1 Ultra 公告中,苹果介绍了 Mac Studio 是如何在全新定制芯片的加持下,让 UltraFusion 芯片之间实现 2.5 TB/s 的互连带宽、以及让两个 M1 Max SoC 协调通信和工作的。现在,芯片代工合作伙伴台积电(TSMC)又证实 —— M1 Ultra 并未采用基于硅中介层的 2.5D 中介层封装工艺(CoWoS-S)、而是更能降低成本的扇出(InFO)与本地硅互连(LSI)方案。

WCCFTech 指出,尽管市面上有多种基于桥接器的方法来让两枚 M1 Max SoC 实现互通,但台积电的 InFO_LI 封装工艺可显著降低芯片制造成本。

此前这家代工厂的 CoWoS-S 封装方案,已被包括苹果在内的诸多合作伙伴所采用,起初许多人推测 M1 Ultra 也会沿用。

然而据 Tom’s Hardware 报道,半导体封装工程专业人士 Tom Wassick 刚刚重新分享了一张幻灯片,指明苹果这次选用了 InFO_LI 封装方案。

虽然 CoWoS-S 已经过验证,但这种封装工艺的应用较 InFO_LI 更昂贵。抛开成本不谈,苹果似乎也没有必须选择 CoWoS-S 的必要。

毕竟 M1 Ultra 仅用于两枚 M1 Max 芯片的互通,而其它组件(包括统一内存、GPU 等组件)都属于硅芯片的一部分。

换言之,除非 M1 Ultra 用到了更多的芯片设计和更快的存储(比如 HBM 高带宽内存),否则 InFO_LI 仍是更明智的选择。

文章来源:电子工程世界

![]()