运算密度跟不上因特网流量增加速度,数据中心分析之数据量的成长速度前所未有;要解决这个问题,需要更大的内存带宽,而这是3D芯片堆栈技术展现其承诺的一个领域。

被甲骨文(Oracle)取消的一个微处理器开发项目,在传统制程微缩速度减缓的同时,让人窥见未来高阶芯片设计的一隅;该Sparc CPU设计提案的目标是采用仍在开发的芯片堆栈技术,取得越来越难透过半导体制程技术取得的优势。

在上述概念背后的研究人员,是甲骨文在今年初被裁撤的硬件部门之一员;但他的点子化为一家顾问公司而存活了下来,并且已经开始与美国硅谷的半导体业者进行合作。 甲骨文前任资深首席工程师、创办了一家三人新创公司ProPrincipia的Don Draper表示:「我看得越深,越觉得这是一条可以走的路。 」

Draper指出:「运算密度跟不上因特网流量增加速度,数据中心分析之数据量的成长速度前所未有;要解决这个问题,需要更大的内存带宽,而这是3D芯片堆栈技术展现其承诺的一个领域。 」

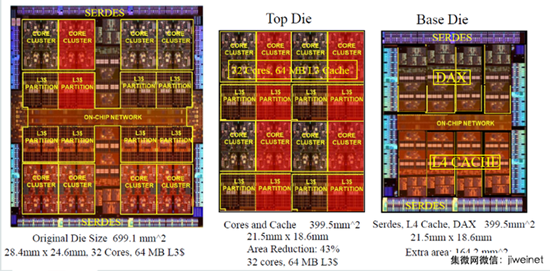

在一场去年底举行的研讨会上,Draper展示了现有的Sparc处理器如何能重新设计成两颗尺寸较小、相互堆栈的裸晶;其中一颗只有处理器核心与高速缓存(caches),另一个则是以N-1或N-2制程节点制造,以一半数据速率运作,乘载串行器-解串行器(serdes)等周边,以及L4高速缓存与芯片上网络──可降低成本与功耗。

Draper表示,新架构芯片的核心数量与L3高速缓存也能增加近一倍,特别是如果堆栈技术采用新兴的微流体冷却(microfluidic-cooling)技术:「在相同的技术节点,可以将性能提升两倍。 」

一颗大型CPU能被重新设计成两颗成本较低的芯片,并取得在功耗、性能方面的优势

高风险却适用机器学习的设计提案

Draper并指出,新兴的芯片堆栈技术是将一个主处理器与一个加速器绑在一起、以因应内存密集任务例如机器学习应用的理想方案;而相反的,若采用芯片对芯片互连例如CCIX与OpenCAPI:「就像在用吸管吸汽水。 」 此外Draper也建议在后缘的裸晶采用整合式稳压器(integrated voltage regulator,IVR);他估计,采用相对较小的磁性电感(magnetic inductors),该IVR能节省功率以及电路板站为面积,并将芯片的数据传输速率提升到150MHz。

尽管如此,Draper坦承,这个他在甲骨文提出的设计提案,也就是在最顶级的M系列处理器采用芯片堆栈技术,是非常高风险且巨大的承诺;举例来说:「如果在(芯片堆栈)实作过程中出了任何问题,最顶端的裸晶可能就会无法使用。 」

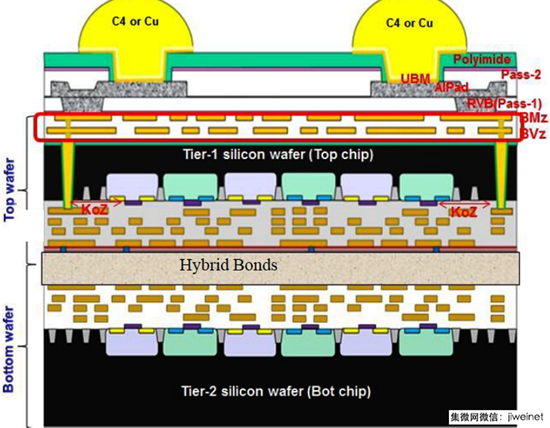

该芯片堆栈采用内存堆栈使用的硅穿孔(TSV)技术,该结构是规律的,但对于高密度、不规则的逻辑芯片来说会很棘手;TSV在厚度上也相对较高,在周遭也需要有保留区域。 Draper声称,芯片堆栈的散热问题大部分可以被解决;具备高导热性的铜接口能轻易地将热从温度较高的顶部裸晶,透过散热片或是风扇从对温度较低的底部裸晶排出。

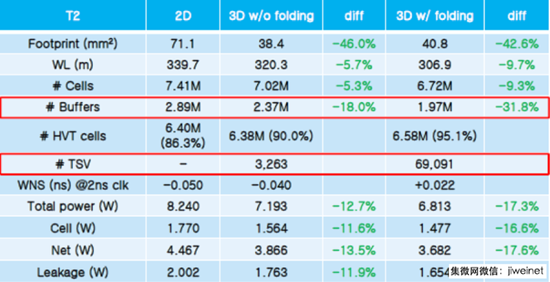

Sparc T2处理器重新设计为两颗中型尺寸芯片,能将功耗降低17.3%

Xperi (编按:原为Tessera)旗下的Invensas,在室温晶圆/裸晶堆栈技术方面是领导者;其技术也是新创公司ProPrincipia创办人Don Draper认为微处理器设计工程师将会用到的。 Invensas的DRAM堆栈可望在2019年量产,接着是处理器、ASIC、GPU与FPGA等各种组件。

Invensas总裁Craig Mitchell表示:「我们现在的目标是与客户沟通,取得他们的晶圆片,因为每个人的制程与硅穿孔(TSV)技术都有点不太一样。 」

另一个障碍是避免晶圆切割时产生的微小颗粒污染;他指出:「我们正在取得良好的进展,能展现4层的DRAM堆栈;另外我们正以3D DRAM为出发点,因为这是一个大规模的市场,而且如果你能在DRAM领域证实技术,将技术转移到任何地方就会容易许多。 」

Invensas是为Sony等厂商采以6~14微米间距的晶圆对晶圆技术接合氧化物,来堆栈CMOS影像传感器而立足市场;在明年某个时候,Invensas预期能迈向下一步,提供能封装一组MEMS传感器的制程技术。

接下来Invensas则将提供新开发的裸晶等级直接结合互连(die-level Direct Bond Interconnect,DBI),以链接传感器与逻辑芯片;该技术已经授权给具备一座大型MEMS晶圆代工厂的Teledyne Dalsa。 最终Invensas的目标是让DBI互连能小于1微米,好将大型芯片转换成相互堆栈的小芯片数组。

Draper展示了类DBI芯片堆栈的横切面

也有其他厂商准备进军此一领域,以较低成本的2.5D芯片堆栈技术,将裸晶并排在相对尺寸较大、较昂贵的硅中介层(interposer)上。

例如台积电(TSMC)在不久前宣布,正在开发一个新版本的晶圆级扇出式封装技术,名为整合式扇出封装(InFO),目前应用于手机应用处理器。 此外台积电也将扩展其2.5D CoWos制程,可在约1,500 mm2面积的基板上放最多8颗的HBM2 DRAM。

Mitchell表示,扩展的InFO技术之40微米I/O焊垫与65mm2基板,不会与Invensas采用DBI技术的更大、更高密度芯片堆栈直接竞争。 但市场研究机构Yole Developpement封装技术分析师Emilie Jolivet表示,最近联发科(Mediatek)宣布,将在一款数据中心应用之芯片使用InFO,显示该技术正在伸展触角。

不过Mitchell表示,DBI与InFO式两种完全不同的技术,后者是一种封装技术、将精细节点的芯片链接到较大节点的印刷电路板链路,而DBI则是采用精细链接的芯片对芯片互连。

举例来说,苹果(Apple)的A10应用处理器采用InFO技术,将220微米间距的裸晶接口,转接至印刷电路板的350微米接口;相反的,DBI正被测试应用DRAM之间40微米的触点,可望在未来能堆栈到8层高。

至于英特尔(Intel),则是开发了EMIB (Embedded Multi-Die Interconnect Bridge)技术,一开始使用于大型FPGA链接外部的串行/解串器;Jolivet认为EMIB技术将改变市场局势,并扩大封装技术领域的战场。

而Mitcell则指出,EMIB也不会与DBI直接竞争,并质疑该技术能扩展到多大程度;他表示,DBI目前最大的竞争对手是热压接合(thermal compression)技术,但被限制在25微米以上的互连:「25微米看来是一道难以突破的障碍。 」

Yole Developpement表示,Apple在A10处理器采用的台积电InFO技术,可说是扇出式封装技术发展在去年的一个转折点;最近该机构有一篇报告指出,扇出封装的设备与材料可望取得40%的复合成长率。

![]()