经过多年的发展和沉淀,半导体芯片封装技术已经越来越成熟,如今已有数百种封装类型。而在这数百种封装类型中,扇出型封装日益火热起来,其更被认为是延续和超越摩尔定律的关键技术方案。本文,请跟着小为一起了解一下扇出型封装技术吧。

1 扇出型(Fan-Out)封装市场分析

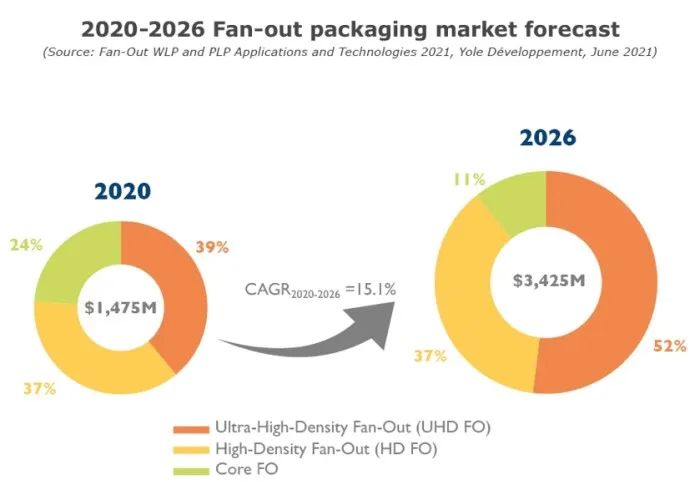

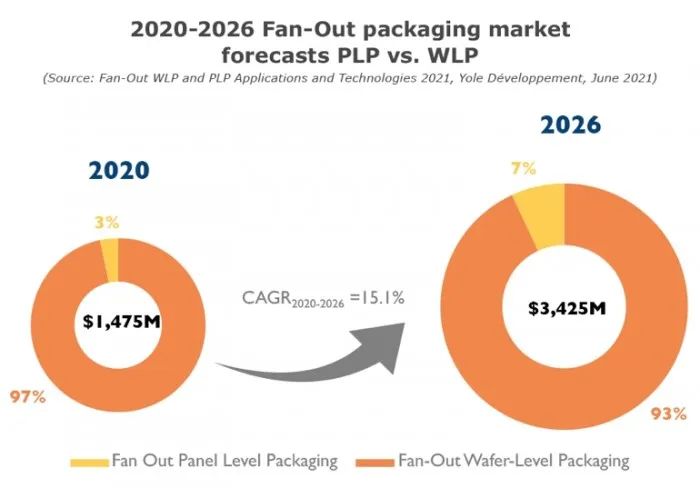

近年来,随着5G、AI和loT的普及,推动了手机、平板、电脑、汽车等多领域发展,同样推动了封装技术的演进,对扇出型封装需求也越来越大,根据Yole 2021年扇出型市场和技术分析报告,扇出型封装增长势头正旺,2020-2026年CAGR为15.1%,市场规模预计从2020年14.75亿美元增长至2026年34.25 亿美元。其中,移动消费领域16.13亿美元,电信与基础设施领域15.97亿美元,汽车出行领域2.15亿美元。

2020-2026年扇出型封装市场发展预期

(图片来源:Yole Development)

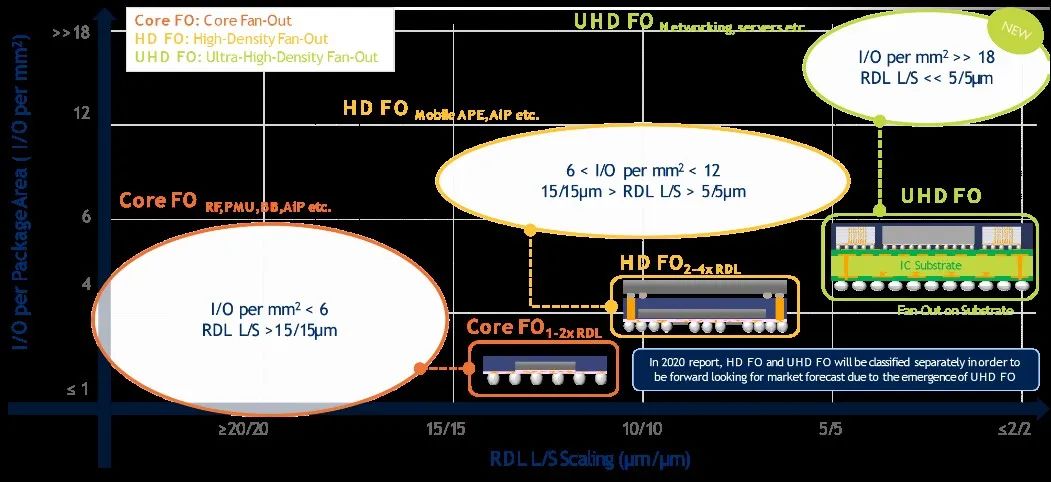

Core FO, HD FO, UHD FO在I/O以及RDL L/S对比

(图片来源:Yole Development)

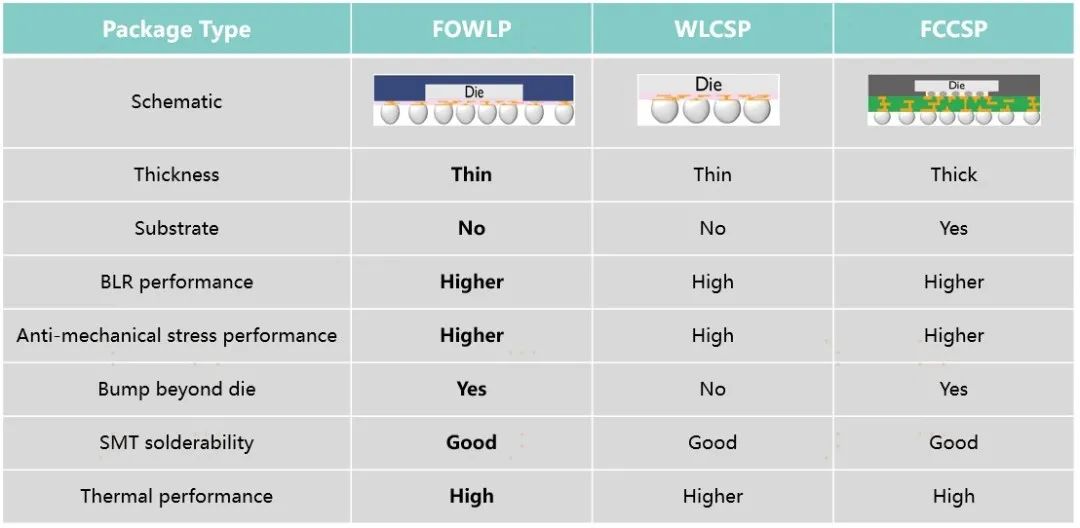

2 扇入型封装和扇出型封装区别

谈到扇出型(Fan-Out)封装,必然会联系到扇入型(Fan-In)封装。扇入型(Fan-In)封装工艺流程大致描述为,整片晶圆芯片进行封装测试,之后再切割成单颗芯片,封装尺寸与芯片尺寸大小相同。

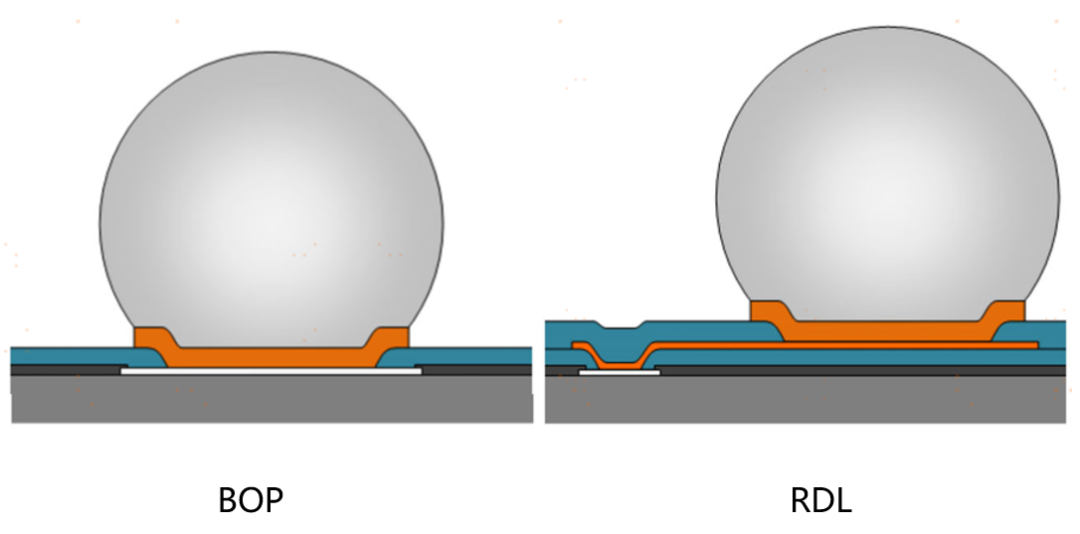

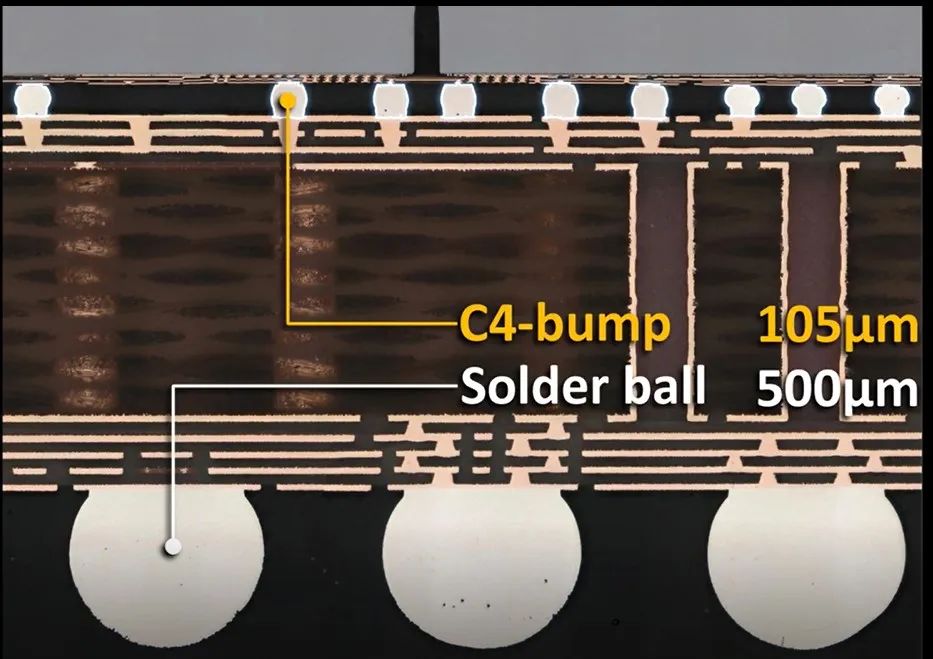

常见的Fan-In(WLCSP)通常可以分为BOP(Bump On Pad)和RDL(RedistribuTIon Layer)。BOP封装结构简单,Bump直接生长在Al pad上;如果Bump位置远离Al pad,则需要通过RDL将Al pad与Bump相连。

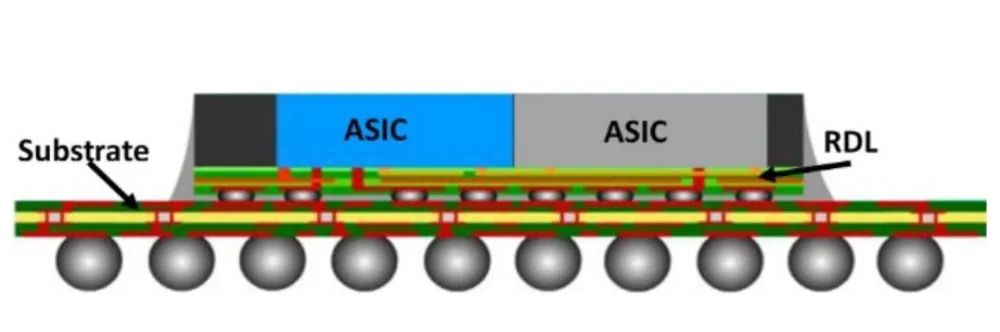

随着I/O数量的增加,芯片尺寸无法容纳所有I/O时,扇出型封装由此衍生而来。扇出型封装基于重组技术,芯片被切割完毕后,将芯片重新嵌埋到重组载板(8寸,12寸wafer carrier或者600mmX580mm等大尺寸面板),按照与扇入型封装工艺类似的步骤进行封装测试,然后将重组载板切割为单颗芯片,芯片外的区域为Fan-Out区域,允许将球放在芯片区域外。

两者最大的差异为RDL布线,在扇入型封装中,RDL向内布线,而在扇出型封装中,RDL既可向内又可向外布线,所以扇出型封装可以实现更多的I/O。

3 扇出型封装细解

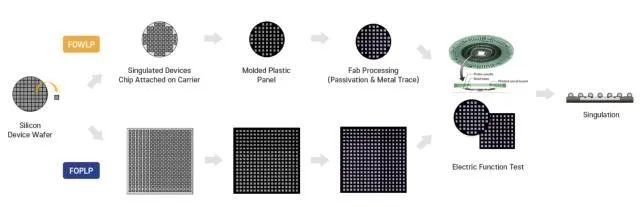

扇出型封装目前存在两大技术分支,即扇出型晶圆级封装(FOWLP)以及扇出型面板级封装(FOPLP)。

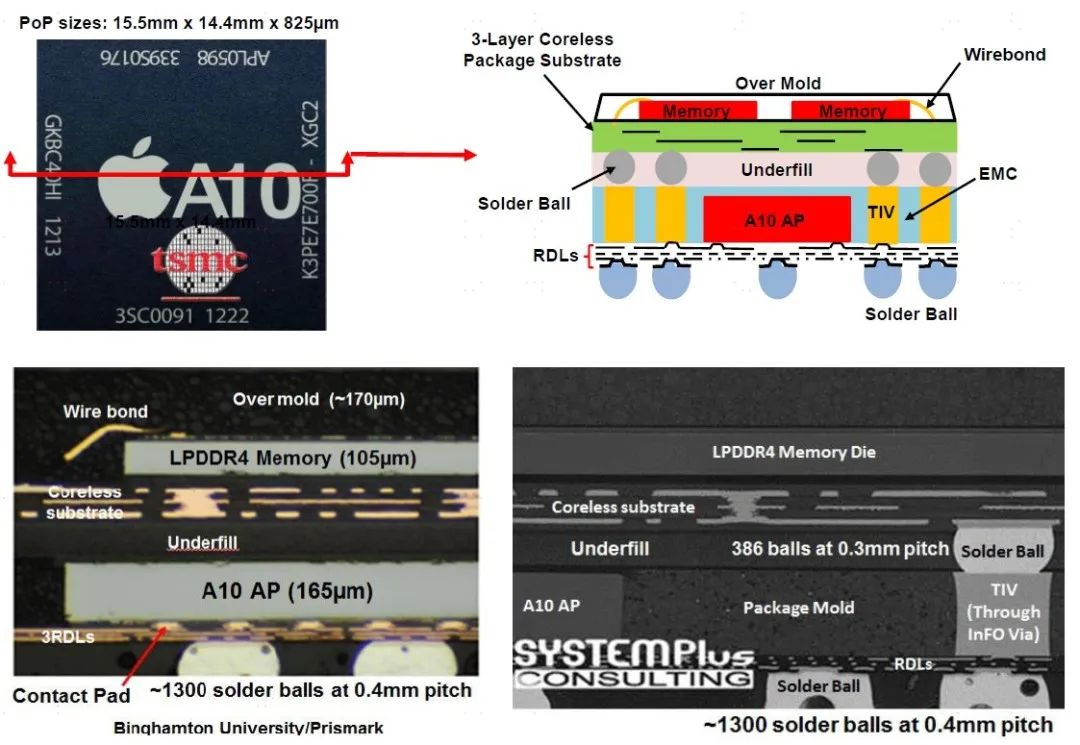

FOWLP封装2009年量产,但彼时只应用于手机基带芯片。真正转折点是2016年,iPhone7系列A10处理器采用TSMC基于FOWLP开发的集成扇出型芯片堆叠(Integrated Fan-Out Package on Package, InFO-PoP)封装,此后扇出型(Fan-Out)封装成为热点,各大手机OEM厂商争相追求HDFO(High-Density Fan-Out)封装。

FOWLP与FOPLP工艺对比

iPhone7系列A10处理器InFO-PoP

(图片来源:TSMC)

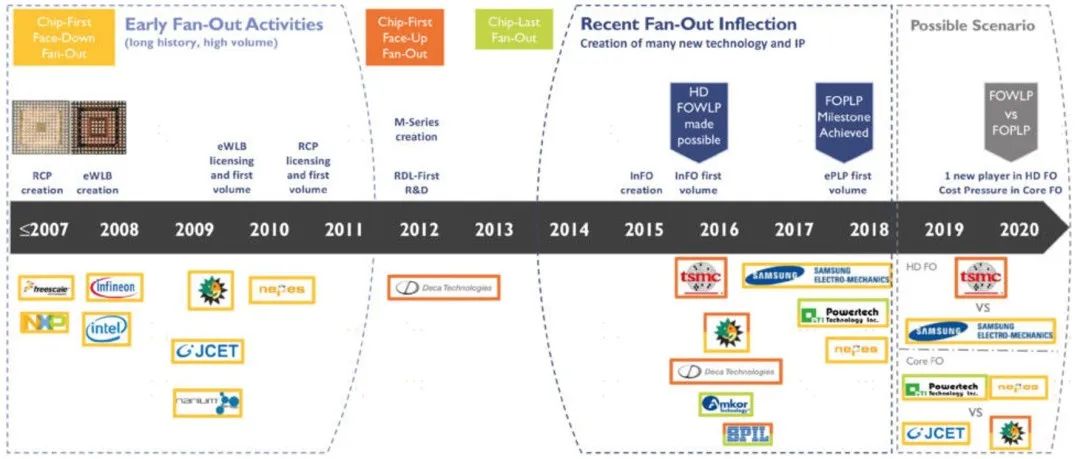

扇出型封装技术演进

(图片来源:Yole Development)

3.1 FOWLP封装技术

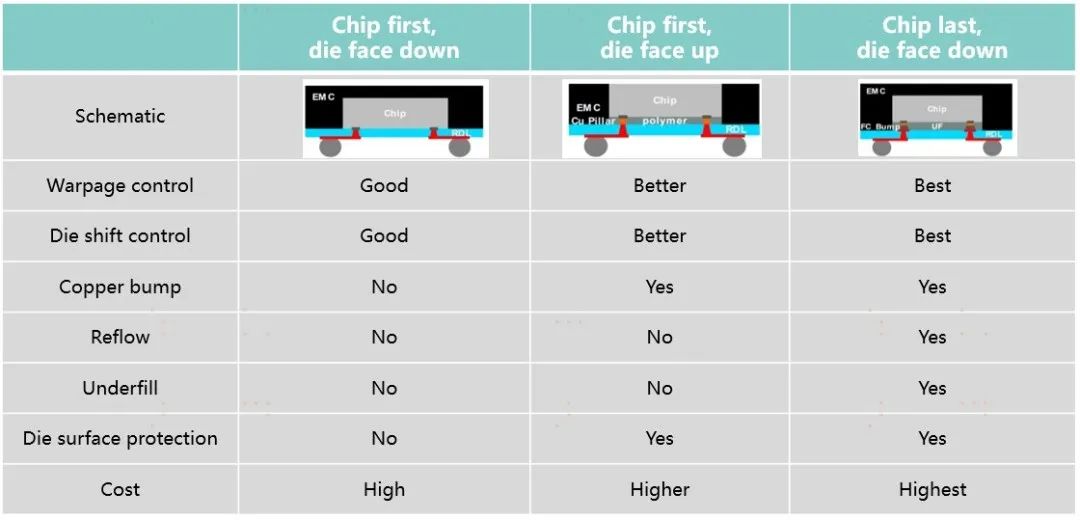

FOWLP封装技术主要分为Chip first以及Chip last,而Chip first可再分为Die face up(如Deca Technologies M-Series封装)以及Die face down(RCP以及eWLB封装等),Chip last形式又被称为RDL first,大致封装流程可参考下图:

☆Chip first, die face down封装技术

飞思卡尔于2006年左右推出重分布封装(ReconsTItuted Chip Package:RCP),英飞凌于2007年左右推出嵌入式晶圆级BGA(Embedded Wafer Level BGA : eWLB)。

RCP与eWLB均为Chip first,dieface down封装,工艺流程类似,与eWLB不同的是,RCP包括一个铜框架层,有助于改善wafer molding过程中芯片偏移,另外可提供电磁屏蔽和散热。

RCP封装

eWLB封装

日月光自研的FOCos(Fan-Out Chip on Substrate)封装同样支持Chip first, die face down封装技术。

FOCos-CF封装(图片来源:ASE)

☆Chip first, die face up封装技术

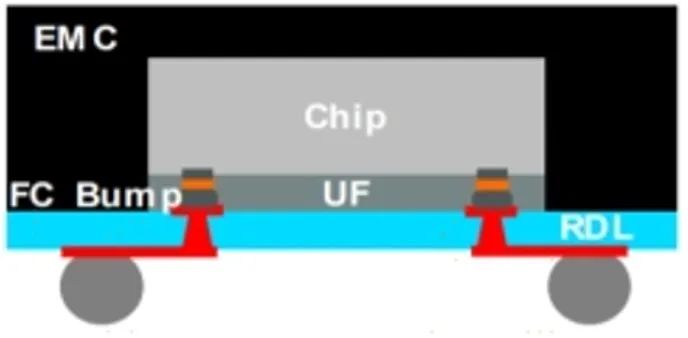

M-Series封装技术由Deca Technologies提出,TSMC于2016年推出的InFO封装,同样采用Chip first, die face up封装技术。

M-Series封装

(图片来源:Deca Technologies)

Chip first, die face up主要优点:

(1)芯片背面贴DAF重组,贴装后偏移较小;

(2)芯片背面贴装,避免了Chip first, face down情况下芯片边缘由切割引入的不平整贴装问题;

(3)更加平坦化,Wafer molding后进行Grinding研磨动作,消除了从芯片表面到Molding compound表面的不平整性。

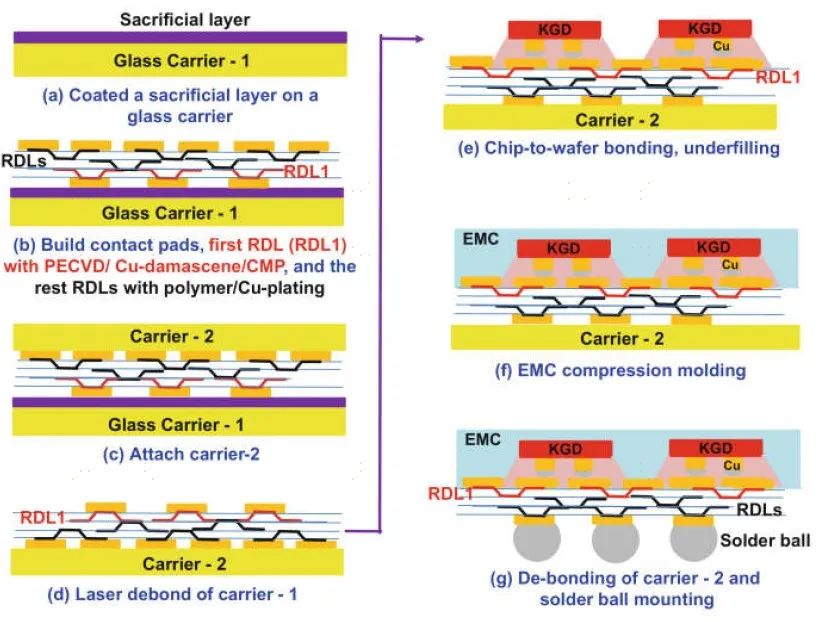

☆ Chip last(or RDL first), die face down封装形式

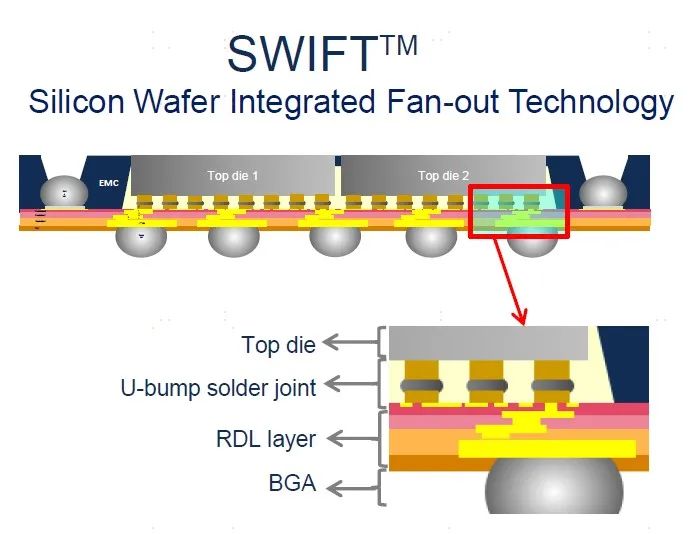

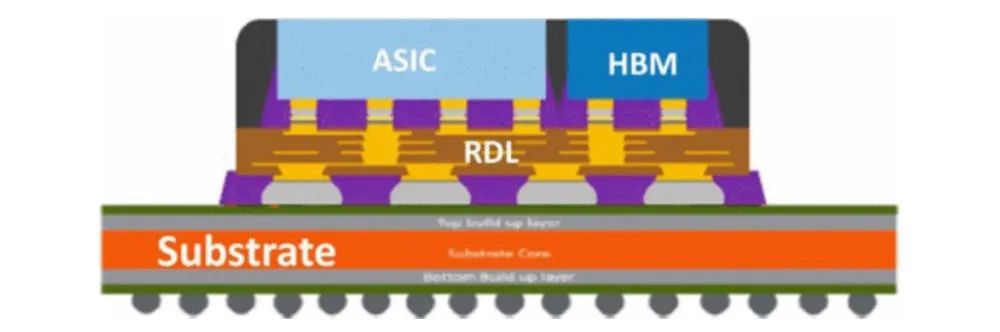

2006年左右由NEC Electronics CorporaTIon提出,Amkor于2015年推出的SWIFT(Silicon Wafer Integrated Fan-Out Technology)封装采用RDL first技术,RDL线宽线距能力≤2um,μbump pitch 40um,SWIFT封装可实现多芯片集成的3D POP封装以及无需TSV(TSV-Less)具有成本优势的HDFO高密度扇出型封装,适用于高性能CPU/GPU,FPGA,Mobile AP以及Mobile BB等。

Chip last, die face down

SWIFT封装

(图片来源:Amkor Technology)

Fan-In PoP SWIFT

(图片来源:Amkor Technology)

SWIFT on Substrate

(图片来源:Amkor Technology)

日月光自研的FOCos(Fan-Out Chip on Substrate)封装同样支持Chip last, die face down封装技术。

FOCos-CL封装

(图片来源:ASE)

Chip last(or RDL first), die face down主要优点:

(1)芯片只会在合格的RDL上倒装芯片,可避免芯片损失,适用于高价格的高端芯片;

(2)芯片通过倒装方式直接与RDL连接,消除了芯片偏移问题;

(3)超细RDL线宽线距实现HDFO,RDL线宽线距能力≤2um。

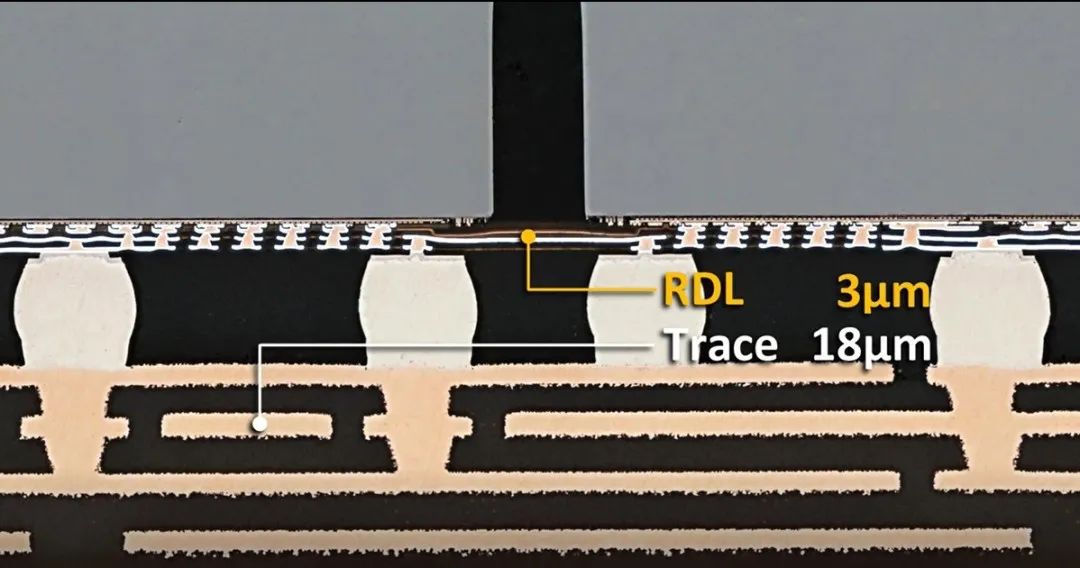

RDL制作方式可分为3种:第一种方式是通过PECVD制作SiO2或者SiN介电层以及Cu大马士革方法制作RDL,RDL线宽线距能力≤2um;第二种方式是通过Polyimide制作介电层以及电镀铜制作RDL,RDL线宽线距能力>2um;第三种方式结合了前两种方式,又称为Hybrid RDL。

Hybrid RDL FOWLP工艺流程

(图片来源:Fan-Out Wafer-Level Packaging)

☆FOWLP封装技术优势

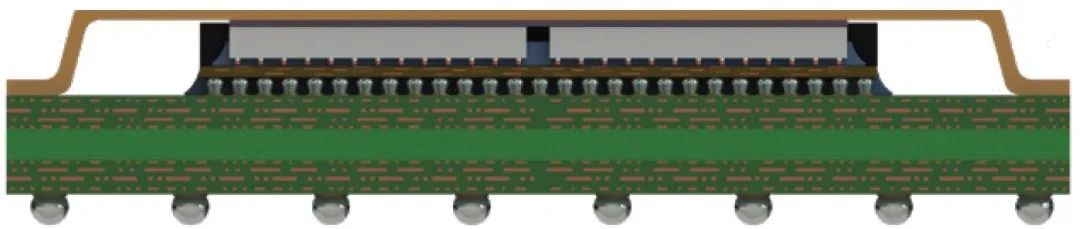

☆FOWLP封装技术对比

☆ 支持FOWLP封装技术主流公司

目前业内主流封装厂以及TSMC都基于不同的技术特点开发出各自的FOWLP技术,如下图所示。艾为基于自身产品的特点以及封装厂的技术优势,很早就已经开始关注FOWLP技术,并已经开始在一些产品上采用部分封装厂的FOWLP技术,艾为目前采用FOWLP封装技术的产品主要应用在电压转换器、音频功率放大器、负载开关等。

3.2 FOPLP封装技术

FOPLP封装流程与FOWLP类似,重组载板由8寸/12寸wafer carrier转换为大尺寸面板,以610mmX457mm尺寸面板为例,面积为12寸wafer carrier的3.9倍,单片产出数量为FOWLP的3.9倍,成本优势较大。

艾为也对FOPLP封装技术的发展保持着高度的关注,目前也已经开始在部分产品上尝试FOPLP技术,在不久的将来也会推出基于FOPLP封装技术的产品。

根据Yole对FOWLP以及FOPLP市场预测,FOWLP目前仍为扇出型(Fan-Out)封装主流,FOPLP正处于平稳增长阶段,预计市场占有率将由2020年的3%提升至2026年的7%。

2020-2026年FOWLP与FOPLP增加预测

(图片来源:Yole Development)

4 扇出型封装展望

扇出型(Fan-Out)封装等先进封装成为延续摩尔定律的关键封装技术,也为Chiplet技术提供了很好的基础,可实现芯片体积微小化以及多芯片高密度集成,扇出型(Fan-Out)封装关键挑战点在于更小的微凸块间距(μbump pitch: 40um-30um-20um-10um),新型键合方式(TCB&NCP, TCB&NCF, Hybrid Bonding等),以及更大的互连密度(RDL L/S: 2/2um-1/1um-0.5/0.5um)。

![]()