跳至内容

半导体的传统指标在最先进的设计中变得越来越没有意义。装入一平方厘米的晶体管数量只有在它们可以被利用的情况下才重要,如果不能为所有晶体管提供足够的功率,每瓦的性能就无关紧要了。

半导体的传统指标在最先进的设计中变得越来越没有意义。装入一平方厘米的晶体管数量只有在它们可以被利用的情况下才重要,如果不能为所有晶体管提供足够的功率,每瓦的性能就无关紧要了。

整个芯片行业的共识是,每个新工艺节点的每个晶体管的成本都在上升,但需要考虑的变量太多,没有人能确定具体是多少,甚至在所有情况下都是如此。随着设计越来越针对特定领域进行定制,直接比较几乎是不可能的。虽然晶体管密度继续增加,但它不再在每个新节点上翻倍。即使在冗余比例很高的大规模并行设计中,通过缩小功能获得的至少一些空间也用于更粗的线路,以防止关键数据路径中的过热、控制器逻辑或某些可能的特殊功能仅适用于单个应用程序或特定用例。

英特尔副总裁兼产品和设计生态系统支持总经理 Rahul Goyal 表示:“这一切都取决于定制工作负载和定制芯片,以及我们将如何设计它们并针对特定应用对其进行验证。” “这是一种更针对特定应用的模型,因为它太贵了,无法满足所有人的需求,并且要为每个应用提供完美的、经过充分验证的芯片。你真的必须回到用例范式。”

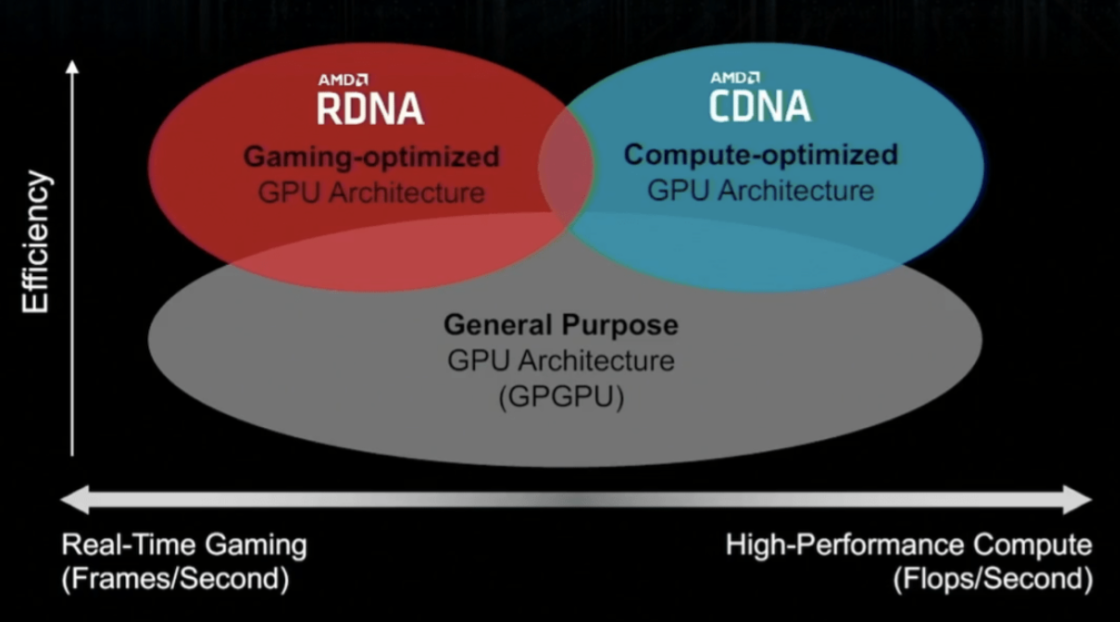

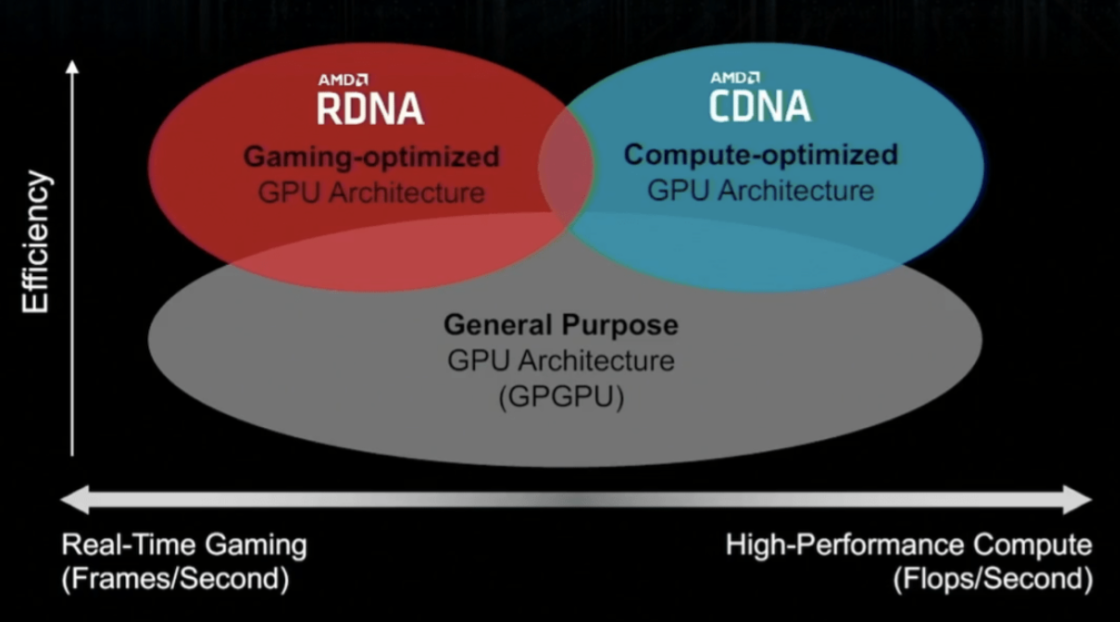

图 1:特定领域架构的兴起。资料来源:AMD/热芯片 34

每个设计都有独特的约束,更高级的设计通常有更多的约束。例如,在 5nm 或 3nm 芯片中,仅仅为数十亿个紧密封装的晶体管供电是很困难的。并且根据架构和布局,热密度可能太高而无法同时使用它们。但它们可以根据需要动态打开和关闭,这种方法可以防止过热并延长芯片的预期寿命。

或者,可以在芯片背面布线以缓解一些拥塞。这增加了制造和包装的复杂性以及成本。但是选择最好的方法取决于应用程序,而传统的指标没有帮助。

台积电业务发展副总裁 Kevin Zhang 表示:“背面供电已经进行了相当长的一段时间。” “问题仍然是复杂性和收益之间的权衡。我们认为 2nm 可能是合适的集成点。您必须以某种方式将其翻转以处理另一侧,有时您必须减薄晶圆以从另一侧建立连接。因此存在机械挑战,也存在热挑战。”

简而言之,芯片设计正在成为一系列复杂的权衡和实验,一个尺寸不再适合所有人。它需要在设计流程的早期进行更多的规划和实验,在验证和调试阶段进行更多的模拟、仿真和原型设计,并在制造过程中将更多的时间花在各种工艺上——测试、计量、检查、蚀刻和沉积,通常使用多个相同(或相同类型)设备的插入点。即使将完全相同的设计迁移到下一个工艺节点,也需要在每个级别进行更多的工程设计,以及更多的工艺步骤。并且根据不同市场中芯片的预期寿命,需要在系统的背景下随着时间的推移查看成本,而不是使用基于晶体管数量、每瓦性能、功耗、交付和由此产生的热效应是普遍关注的问题,它们影响从设计到制造流程的每一步,从平面规划到材料。

“当您必须为较低的后端层供电时,事情会变得更加困难,因为您的线路非常细,并且您必须从分布良好的均匀电网过渡到电路的极其特定部分,”副总裁 David Fried 说Lam Research的计算产品。“这是我们开始看到很多挑战的地方。由于我们在过去 20 年中了解了铜后端中的电迁移、应力迁移和 TDDB(时间相关介质击穿),我们在 M0 和 M1 中创建了相对较厚的衬垫,以便铜可以成功使用用于配电。归根结底,随着您的生产线缩小,您最终会在这些较低的后端生产线中使用更多的衬垫和更少的铜。这些线现在主要是衬里,这些衬里的阻力要高得多。我们开始看到无衬垫方法的引入,包括超薄衬垫或使用不同金属的薄屏障。”

十多年来,芯片制造商已经看到了这种转变。英特尔于 2013 年获得了钴互连及其制造方法的专利。从那时起,钴已被用于从触点和互连到沟槽衬垫的所有领域,代工厂和大学正在进行更多的实验,以帮助处理与动态功率密度增加和静态电流泄漏相关的热量。

“互连变得越来越重要,”台积电的张说。“有创新的方法,包括新材料。如果您考虑铜线,则大部分电阻实际上来自阻挡层。可以降低阻挡层电阻的新材料非常非常重要。我们的研发团队正在积极探索诸如低k材料和气隙之类的东西,以进一步减少寄生效应。”

在制造过程中很少引入新材料,因为它们需要在大批量制造中得到一致部署和验证,通常与其他工艺结合使用。工艺工程师仍然对他们在 2000 年遇到的困难感到畏缩,当时他们在 130nm 用铜代替铝互连。做出这些改变一定有很好的理由,而探索是一个持续的过程。

“钴具有比铜更高的体电阻,但由于您可以使用更薄的衬垫,您可以将更多的钴放入插头或线路中,”弗里德解释说。“因此,即使钴具有更高的体积电阻,您可以将更多的钴加入生产线这一事实总体上会降低线路或插头的电阻。您将看到一些新金属的使用,例如钼,它开始被更频繁地使用。不幸的是,这并不是说我们要用其他金属代替铜那么简单。芯片上有特定的插入点,材料的成本——以及材料的集成——在电路效益方面是合理的。”

这些理由的定义越来越狭隘。在性能规模的高端,最大的数据中心由谷歌、亚马逊、Meta、百度和阿里巴巴等公司运营,这些公司现在都设计自己的处理器来处理内部开发的算法。在 PC 和智能手机市场,Apple 设计了与软件紧密集成的处理器,与以前的现成芯片设计相比,它大大延长了电池寿命。MacBook 电池在两次充电之间持续 20 小时或更长时间并不罕见,而过去是 5 小时。

但这些指标对每家公司都是独一无二的,设计和测试这些复杂芯片所需的成本不再孤立地看待。处理器现在被认为是更大系统的战略部分,它们可能包括各种组件,从 CPU 和 GPU 到 NPU。并非所有这些都需要在 5nm 或 3nm 上开发,也不是所有这些都需要一直使用或用于关键功能。

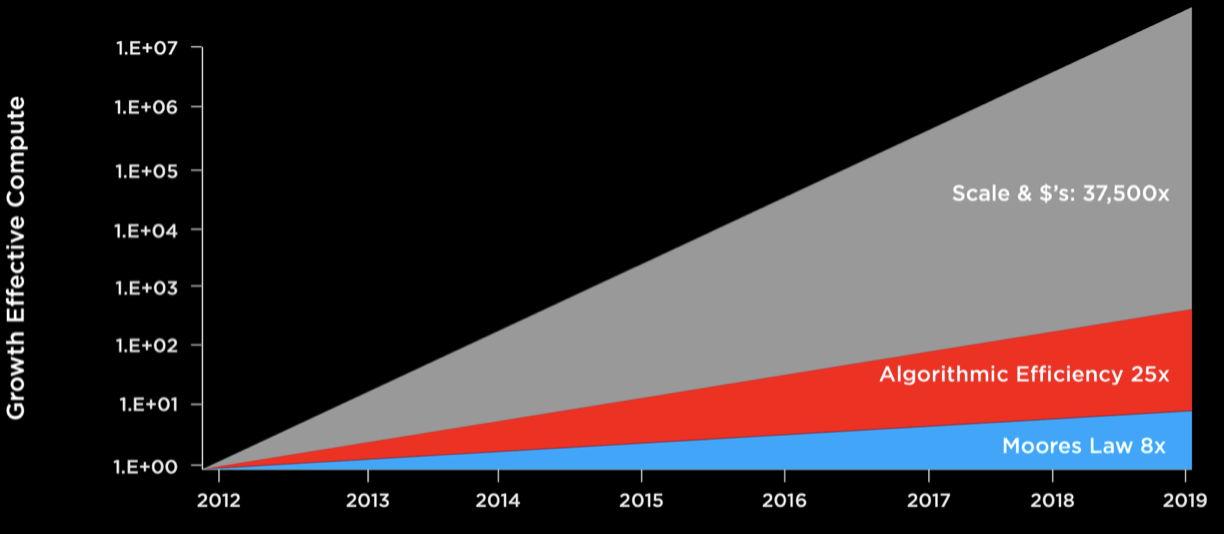

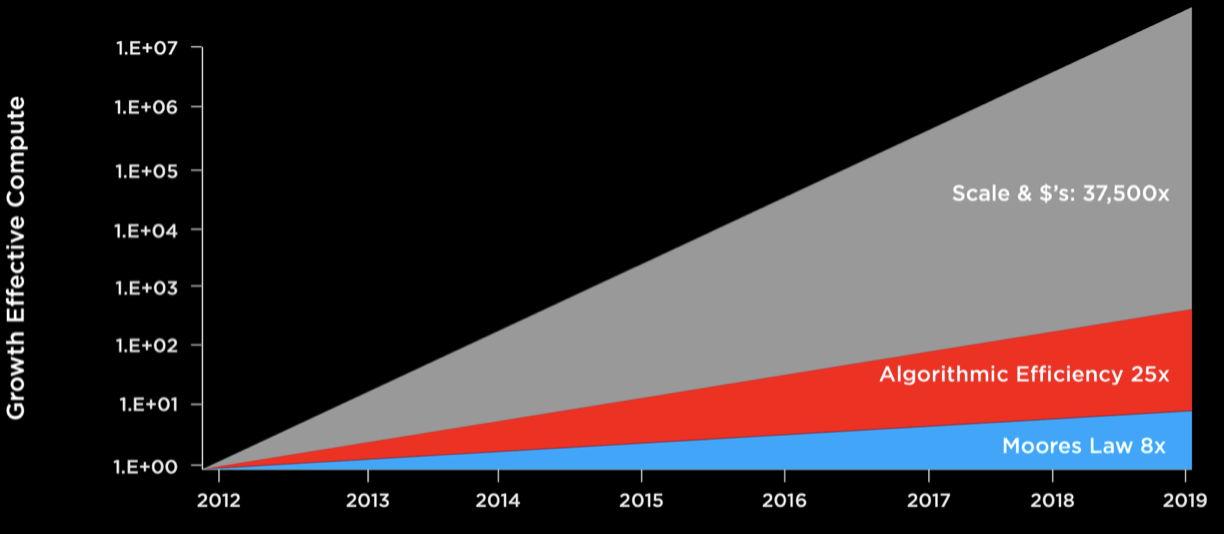

图 2:随着时间的推移有效计算的不同指标。资料来源:特斯拉/Hot Chips 34

尽管如此,它们都需要按预期工作,并且传统上以产量来衡量。但是有一些方法可以在不生产完美芯片的情况下保持良率。可能有足够的冗余来抵消错误,或者有足够的弹性来允许它在规范内运行。因此,传统上可能被认为是糟糕的芯片可能仍然足够好。

“没有什么是完美的,”imec 3D 系统集成项目高级研究员兼主任 Eric Beyne 说。“有一定程度的故障可以通过某些测试,这不一定是戏剧性的,因为您稍后会在功能测试中发现它们。所以有“足够好”的测试。并且可以存在冗余,例如总线接口,它们可以具有用于错误编码的冗余线路。当然,这是以延迟和复杂性为代价的。你可以将你的接口设计成容错的,但在某种程度上你会付出代价。这就是这里的重大权衡。要么是成本,要么一切都如你所愿地完美运行。”

这并不意味着不适合一种应用的芯片也不能在其他地方使用。“某些市场将需要不同的兼容性门槛,” Onto Innovation软件产品管理总监 Mike McIntyre 说. “人们多年来一直在构建内存立方体,而那个内存立方体具有一定的性能阈值。但是该性能阈值是由该堆栈中最低的芯片性能设定的。因此,如果您在该堆栈中拥有所有高速内存,它将是一个高速等效的芯片堆栈。但是如果你把一个低速内存芯片放在那里,整个堆栈就会受到那个芯片的性能的限制。这也发生在系统级别。您是否有进入高性能市场的系统的优质芯片?或者您是否有可以投入一般市场的鲜为人知的芯片质量?因此,它可能是服务器、笔记本电脑和其他一些实用计算系统。”

“某些技术适用于某些解决方案或某些问题,”imec 的 Beyne 说。“并不是说他们会无所事事。对于像扇入、扇出和系统级封装这样的东西,有一整套有用的技术。这实际上取决于您要解决的问题。如果您考虑手机中的射频模块,那些所谓的芯片可能是一个封装中的 50 个不同组件的集合,但这些组件相对而言很少有连接。所以互连密度低。你不能对 AI 内存逻辑分区做同样的事情,这是非常不同的。”

然而,越来越明显的是,芯片行业的大部分活动并没有发生在前沿节点上,这些指标提供了关于晶体管数量或自动功率、性能和面积/成本优势的吹嘘权利。具有讽刺意味的是,对指标的大多数担忧都发生在更成熟的节点上,尤其是小芯片和先进封装,以及可能适用于汽车等应用的芯片。

在包装方面,有很多可能的组合,以至于指标变成了分布和概率,而不是固定的数字。Brewer Science首席开发官 Kim Arnold 表示:“先进的包装不仅可以灵活地打开和关闭事物以使它们融合在一起,而且还可以设计不同的方式使事物融合在一起。” “我们的空间将会发生很多变化。现在的问题是,在所有可能的途径中,哪些将成为赢家,哪些将成为利基市场。”

今天很难确定这一点,因为全面的活动如此之多。边缘的构建以及所有将利用边缘计算的设备——汽车、工业设备、物联网设备、智能手机——正在为每个人创造足够的工作,从前沿到成熟的节点。这在联华电子与分析师的第二季度财报电话会议中很明显。“我们相信 28 和 22 [nm] 将是持久的节点,并得到非常多样化的产品组合基础的支持,”联电首席财务官 Qi Don Liu 表示。“在未来几年,我们预计 28 和 22 的需求将保持强劲,这将受到 Wi-Fi 6、6E、GPON(千兆无源光网络)领域的网络以及 OLED 驱动器应用等应用的推动。”

因此,虽然联华电子仍计划在其产品中添加 finFET,但这并不是当务之急。“我们将继续在 finFET 上取得进展,但从容量部署的角度来看,目前与其他节点相比,它的优先级确实较低,”联电总裁 Jason Wang 说。“我们仍在路线图上放置 14 个,但短期内还没有大规模的容量部署计划。”

这种方法在 GlobalFoundries 得到了回应,它专注于成熟节点的独特实现,而不是在设计少得多的最先进节点上将其扼杀。GlobalFoundries 技术、工程和质量高级副总裁 Gregg Bartlett 说:“特别是设计套件是我们的差异化领域。“因此,即使我们的竞争对手拥有完全相同的晶体管性能,我们也可以通过 PDK 获得更好的产品,因为我们已经与 EDA 公司集成了功能,或者我们已经使用为我们制造更好产品的元素模拟了硅。作为一个硅或材料的人,我总是想根据晶体管性能、更好的驱动电流、更低的泄漏、更高的温度兼容性来区分技术。但越来越多,这是关于设计背景或设计意图。我们投入了大量的 PDK 工作,致力于确保我们客户所需的 EDA 工具能够为他们的设计提供信息。”

最后,可以使用小芯片混合和匹配几乎所有东西。这意味着可以在 3nm 甚至更小的尺寸上创建一个小型逻辑元件,并使用一些现成的或定制的互连方案与同一封装中的 180nm 小芯片集成。这里的优势是三维。这可用于降低各种类型的噪声、改善散热和提高良率,这通常会随着芯片物理尺寸的减小而增加。这甚至允许在某些组件中实现更高的密度,这在过去由于掩模光刻的限制是站不住脚的。

“曲线 ILT能够实现比传统OPC更好的工艺窗口,传统 OPC仅限于曼哈顿 (45°) 形状,” D2S首席执行官 Aki Fujimura 说。“面具形状曾经受到限制,实际上是曼哈顿形状,因为面具是用 VSB(可变形状电子束)写入器编写的。每个技术节点都变得越来越难,即使是 EUV,也越来越难以使晶圆形状在制造变化中尽可能统一。大约 20 年来,通过在面罩上使用曲线形状可以实现最佳均匀性,这一点已经确立。”

虽然芯片制造商和系统公司仍需证明其指标的合理性,但真正的价值要复杂得多,而且要针对特定领域。I/O 的速度对于拖拉机上的传感器可能无关紧要,但对于与基础设施或附近汽车连接的汽车中的芯片可能至关重要。同样,处理速度在用于手机内流式传输视频的芯片中可能不太相关,但它们对于检测高超音速导弹的航向至关重要。

这引发了消费者在未来将如何区分设备的问题,并为系统公司如何将各个部分组合在一起的一系列可能选项打开了大门。但至少在短期内,可能会有更多的混乱。过去 50 年来一直定义芯片架构的指标变得越来越不相关,而真正重要的指标可能过于复杂而无法解释。

![]()

![]()