一年一度的ITC 活动在 9 月的最后一周举行。小芯片、2.5D 和 3D IC 设计已经引起了测试界的关注,Siemens EDA 在ITC上介绍了2.5D 和 3D IC DFT 的最新进展。

DFT 挑战

在 IC 设计的大部分历史中,我们在一个封装中使用了一个芯片,以及多芯片模块 (MCM)。对于具有多个裸片的 2.5D 和 3D IC,您如何进行单个裸片测试,然后使它们适用于最终封装?

如果每个内部裸片的 DFT 架构彼此不同怎么办?

是否有一种最佳方式来安排封装中的芯片测试以减少测试时间?

2.5D 和 3D 小芯片

Tessent MulTI-die

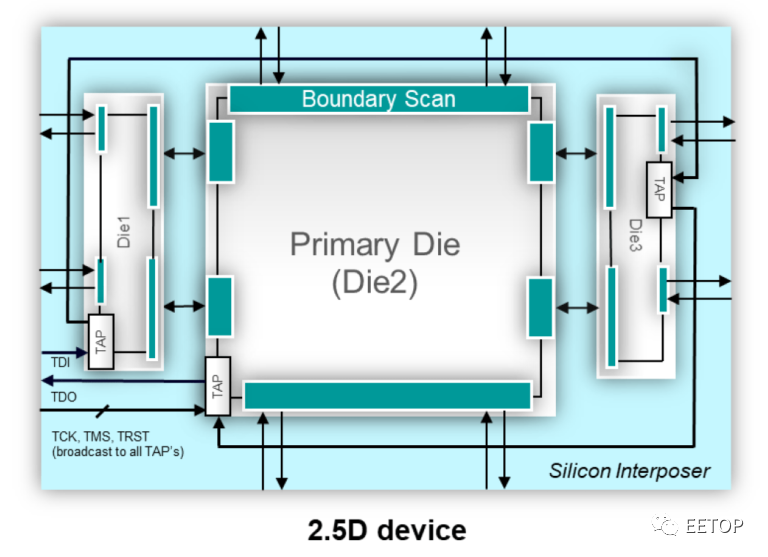

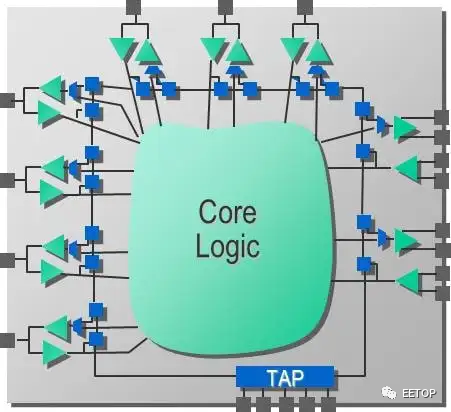

Siemens 的开发团队扩展了他们的技术,使用TessentMulTI-die支持 2.5D 和 3D IC 封装。这种相同的方法现在将 2D 分层 DFT 扩展到 2.5D 和 3D IC。以下是 2.5D 设备中三个小芯片的外观:

IEEE 为 3D 堆叠 IC 的测试访问架构创建了一个标准,称为IEEE 1838-2019。IEEE 1687 使用另一个标准 IEEE 1149.1 定义了对嵌入在 IC 中的仪器的访问和控制——带有测试访问端口。Tessent MulTI-die 支持所有这些标准。

小芯片设计中的每个裸片都有一个边界扫描描述语言 (BSDL) 文件,然后 Tessent MulTI-die 会为您创建封装级 BSDL。

IEEE 1838

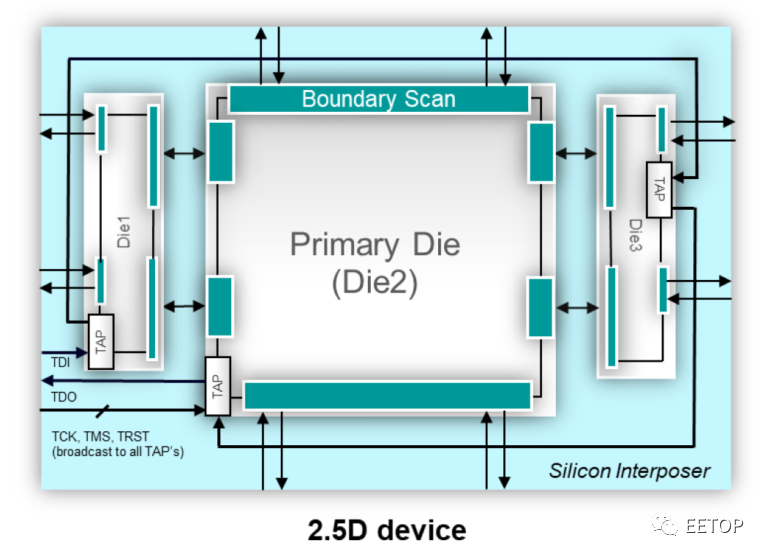

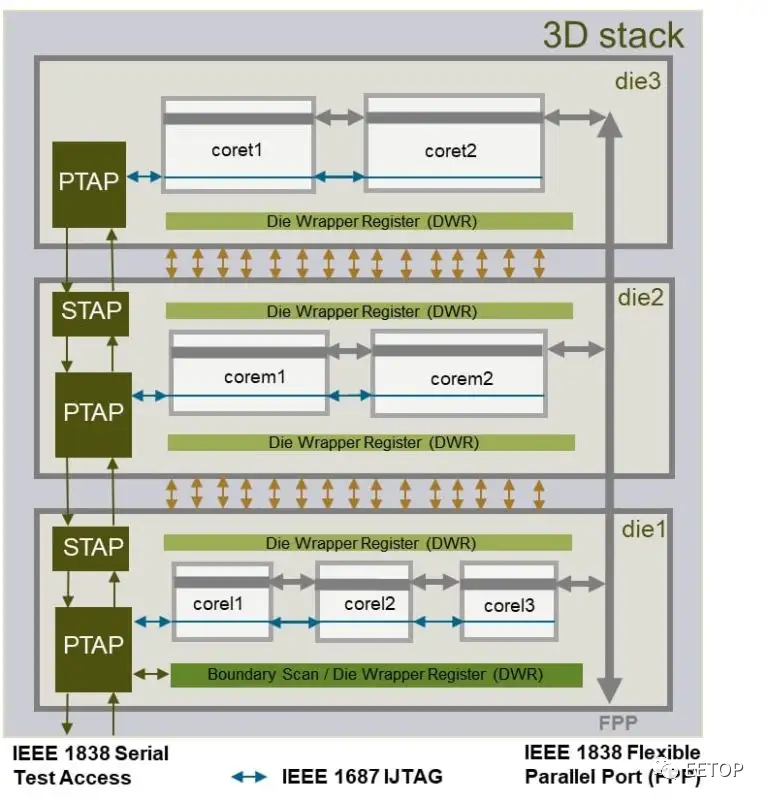

这种以芯片为中心的测试标准于 2019 年 11 月获得批准,并允许将芯片作为多芯片堆栈的一部分进行测试。使用灵活并行端口 (FPP) 以及芯片封装寄存器 (DWR) 和测试访问端口 (TAP) 连接 3D 芯片堆栈以进行测试:

用于测试的 3D 堆栈

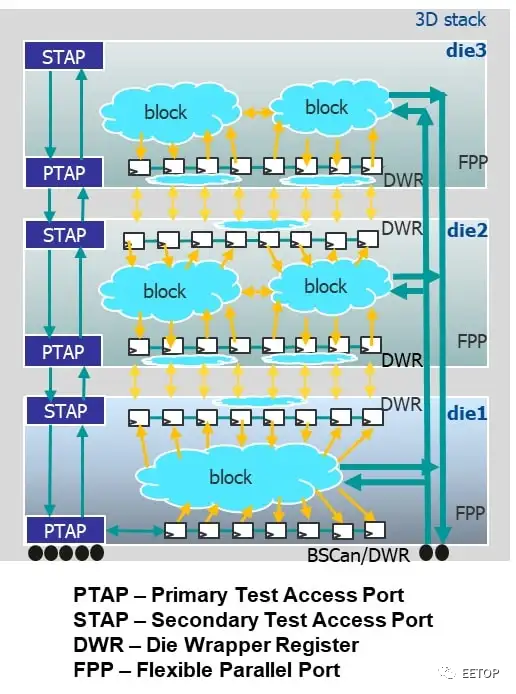

IEEE 1687 – 内部 JTAG

这个 2014 标准有助于简化嵌入在每个芯片中的仪器的使用。有仪器连接语言 (ICL) 和过程描述语言 (PDL) 来定义仪器。ATE 系统和内部 JTAG 之间的流程如下所示:

IEEE 1687 流程

IEEE 1149.1 JTG

带有测试访问端口的边界扫描标准可以追溯到 1990 年,而边界扫描描述语言 (BSDL) 在 2001 年问世。该标准定义了指令和测试数据在芯片内的流动方式。

IEEE 1149.1 JTAG

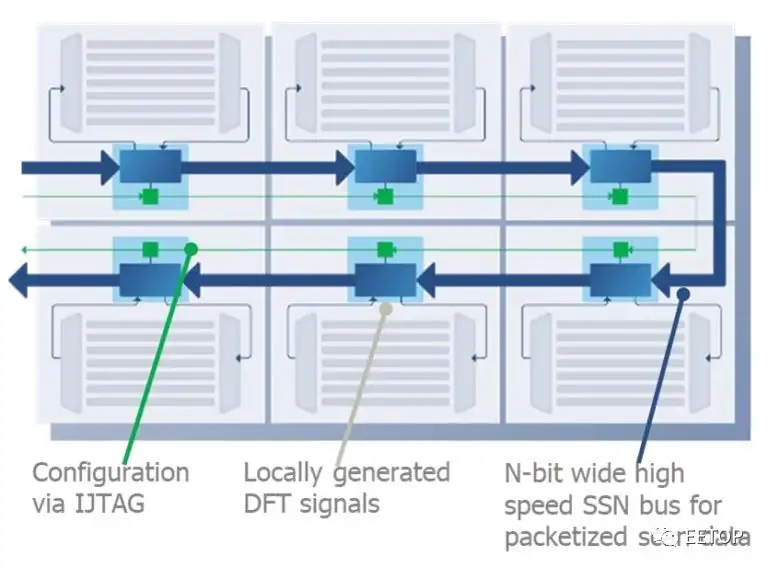

将所有这些测试标准结合在一起,我们可以看到 TessentMulti-die 如何连接到 3D 堆栈内的每个小芯片。每个裸片内内核的测试模式和测试调度是通过 Tessent 流式扫描网络 (SSN) 完成的。

Tessent 流式扫描网络

SSN 基本上将测试数据交付打包,将核心 DFT 和芯片 DFT 解耦,允许同时测试的核心独立转移。实际的好处是节省了 DFT 规划的时间、更容易的布线和时序收敛,以及高达 4 倍的测试时间和体积减少。

Tessent SSN

总结

代工厂、设计、测试和 IEEE 之间的密切合作创造了一个充满活力的 2.5D 和 3D 生态系统,所有技术都已到位,以推动半导体创新。Siemens EDA 扩展了他们的 Tessent 软件以迎接新的测试挑战,同时使用 IEEE 标准。Tessent Multi-die 与所有其他 Tessent 产品和平台集成,因此您不必将工具和流程拼凑在一起。

![]()