传统缩放比例的终结就在眼前,但摩尔定律仍在继续。Imec 的埃里克·贝恩 (Eric Beyne) 强调了未来几年将开启的众多技巧之一:背面供电。

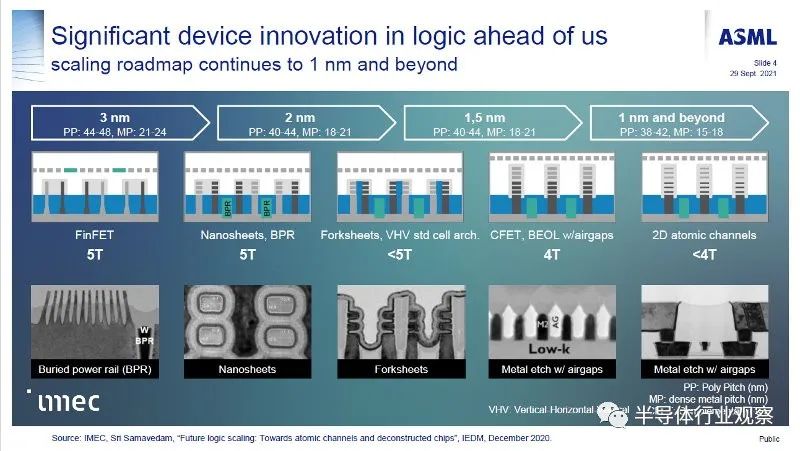

我们这些还没有退休的人将非常肯定地见证:我们所知道的使用当前光刻工具的芯片缩放的终结。大约十年后,我们将最终达到亚纳米结构。当时关于光刻工具的讨论——High NA、hyper NA 或 EUV 的其他一些涡轮变体——并不重要。半导体行业将选择成本最低的途径,继续取得进步,可靠、快速地制造芯片。无论 IC 工艺工程师将使用何种工具,我们都将在未来十年感受到物理限制。

有趣的是,半导体行业的每个人似乎都同意摩尔定律在那之后还会持续一段时间。半导体路线图确实充满了技术和想法,以保持同一芯片表面上更多设备的稳定节奏。系统架构师将更有效地使用可用的硅表面。他们已经掌握了保证原子清晰度和利用三维空间的技术。

去年夏天,在 2022 年 IEEE VLSI 技术和电路研讨会上,Imec 深入了解了一种将帮助芯片架构师在未来几年继续扩展的技术:背面供电。Bits&Chips 去鲁汶听取 Eric Beyne 讲述了他们有关这方面的最新消息。

Eric Beyne 在 Imec 领导背面供电开发项目。

数十年来,Beyne 一直领导着 Imec 对后端芯片技术的研究。他的团队正在推进一个将对前端架构产生重大影响的项目,这表明后端(封装)和前端芯片制造(晶圆工艺)之间的界限正在变得模糊。来自 45 家芯片制造商和设备制造商的 200 名研究人员目前正在 Imec 参与背面供电技术的开发。

将电源倒置

简而言之,芯片由硅衬底和一层有源元件(晶体管)组成。在该有源层上方是绝缘氧化硅矩阵中的一团电线。该布线网络有两个用途:信号和电源。“将所有这些放入同一表面变得越来越困难,”Beyne 总结了背面供电 (BSP) 的关键驱动因素时说。

不断进步的缩放比例尤其使得为有源部件(晶体管)提供正确的功率变得越来越困难。这是一种平衡行为:功耗不应太高,但电压必须足够高才能切换。问题是电源线不仅变长了,而且变细了。

BSP 背后的整个想法是将电源翻转过来,从底部而不是顶部为晶体管提供能量。因此得名,背面供电。

未来会分两期制作带有BSP的芯片。首先是带有有源层的芯片和上面的信号,然后是背面供电传输。一旦处理了微电子的活性层,它下面的几乎所有硅都被去除了。之后,工作开始于底部的微电子网络。

电压线和中性线

载体材料的去除非常严格:几乎整个原始晶圆都消失了。经过打磨、抛光和蚀刻后,会留下大约 100 纳米厚的一层。Beyne:“这会把你带到电路下面。然后,您可以在标准单元级别进行连接。” 标准单元是集成电路的基本块。它们由多个晶体管组成,具有加减法等简单功能。

6 月,Imec 提议通过埋入式电源轨(交流电压和中性线的平行电源路径)为 2nm 芯片一代中的这些基本构建块供电。对于最先进的芯片,这些埋入式电源轨之间的距离约为 200 纳米,但未来将向 100 纳米发展。对于背面供电,其想法是通过背面(或者如果您愿意,也可以是底部)将电源电压和时钟传输到这些埋入式电源轨。

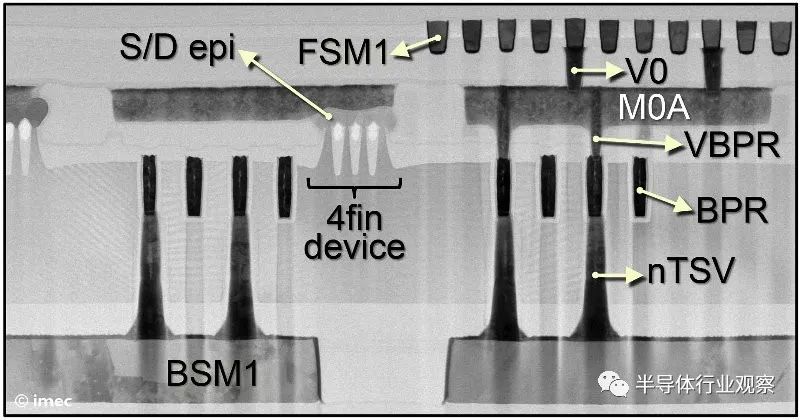

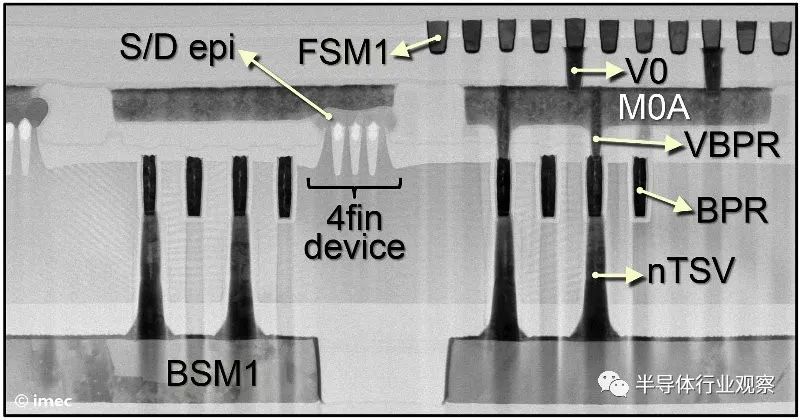

在 2022 年 IEEE VLSI 技术和电路研讨会上,Imec 展示了一种经过处理的背面供电芯片。电源通过纳米硅通孔 (nTSV) 从底部金属层传输到埋入式电源轨 (BPR)。

该操作最初简化了布线方案——晶体管上方的布线。它解耦标准单元之间的电源和信号。同时,这种修改使得芯片架构中的晶体管在物理微米级和纳米级可以更靠近地放置在一起。

十四层金属

随着每一代芯片的出现,路由方案的复杂性都在增加。需要越来越多的金属层,每增加一层就意味着额外的成本。举个例子,台积电生产的 7 纳米逻辑电路有多达 14 个金属层。随着电源和信号的解耦,可以降低成本,当然,将电源连接到背板所需的操作会增加成本。毕竟,打磨、抛光和蚀刻整个晶圆是相当严格的。

但是有很多好处。为了在晶体管级获得功率,当今芯片上的电流必须通过许多金属层。电源的金属线必须尽可能宽和粗,以实现低电阻。它从上方的宽通道到更靠近晶体管的细线。尤其是后面的线路的电阻是有问题的高。

Beyne 说,由此产生的压降让芯片设计师越来越头疼。“电源必须通过意大利面条网络连接到晶体管。由于高压降,晶体管上的 0.7 伏不再是 0.7 伏。电阻太高。电压太低会导致丢失时钟周期,从而导致错误。关键路径必须足够快以在一个时钟周期内切换。这越来越取决于晶体管的电源。”

直接连接电源和时钟

但是,电压越高,功耗就越高(随电压呈二次方增长)。“在某些时候,那里没有任何改进,”Beyne 说。“如果你可以将电源和时钟直接连接到电源阵列,电阻就会低得多。在后端,只有标准单元级别的连接很小。在那之后,你可以直接进入宽金属层,从而获得低一个数量级的电阻。”

埋入式电源轨之间的距离现在为 200 纳米,在未来几代芯片中将达到 100 纳米。与 FinFET 晶体管一样,这些轨道是垂直的。“我们将通过 100 纳米的硅层将它们连接起来。所需的孔直径为 90 纳米,其中我们需要 10 纳米用于绝缘。通过与埋地电源轨的连接,您可以在电源和晶体管之间建立一条直线。”

从 800 微米厚的硅晶片上打磨掉几乎所有材料等操作是有风险的。这个过程需要很好地控制。根据 Beyne 的说法,最粗的打磨可以达到 2 微米的精度。“之后,您可以使用选择性蚀刻剂去除多余的硅,干法和湿法技术均可使用。”

硅锗或氧化硅

蚀刻必须停止的阻挡层可以是例如硅锗或氧化硅。在放置晶体管之前,可以通过外延步骤应用 SiGe。带有氧化硅层的切片可以作为标准,称为绝缘体上硅 (SOI) 晶圆。晶片硅和阻挡层的硅锗或氧化硅之间蚀刻剂的选择性是百分之一。“因此,如果你需要蚀刻半微米,而你过度蚀刻了 500 纳米的硅,你只会损失 5 纳米的阻挡材料。”

高端芯片需要数十亿个连接,称为硅通孔 (TSV)。“它们有很多,所以通过最后一个狭窄连接的电流非常低。” 后端布线不需要高级光刻。“前端光刻,90纳米已经成熟了。”

但这并不意味着布置数十亿个 TSV 是一项简单的工作。Beyne:“如果晶圆不变形,事情就简单了。但是如果你键合两个晶圆,你还必须处理键合过程中晶圆的变形。这是所有晶圆加工都会出现的一个特定问题,就像贴上贴纸时会拉伸一样。你不仅要处理旋转平移,还要处理拉伸和其他变形。”

在 2021 年底的 ASML 投资者日的演讲中,MarTIn van den Brink 已经表明 Imec 期望在 2nm 节点进行背面功率传输。学分:ASML

光刻校正

解决方案必须来自光刻设备,这些有充足的修正机会。“ASML 系统配备了对投影图像进行三阶校正的功能。剩余的 100 纳米层(打磨和蚀刻后,RR)是透明的,因此您也可以从背面看到对齐标记。通过校正,我们达到了 10 纳米的精度,因此您可以将这样一个 90 纳米宽的 TSV 正确地放置在埋入的电源轨上,而不是它旁边的晶体管上——这实际上是一个巨大的挑战。”

与此同时,英特尔宣布了名为“Powervia”的背面供电。这家美国芯片公司将在其 20A 芯片中引入该技术(英特尔在其下一代产品中使用埃而不是纳米)。20A 将于 2024 年或 2025 年投放市场。

对于BPD,整个行业都需要做好准备,包括芯片设计工具厂商。“EDA 工具需要了解芯片地下室而非阁楼中存在连接。” 但是所有主要的半导体公司都在探索这项技术,尽管三星和台积电尚未公开他们的确切计划。

![]()