背景介绍

SIP(系统级封装)在市场上已不再是新鲜事。与 70 年代的电子产品相比,手机、家电等现代电子产品均采用创新型半导体,不仅体积小巧而且功能多样。然而对于半导体制造商而言,电子产品要实现体积更小、多功能、可靠、经济且上市时间更短始终是一个挑战。

为了获得更小巧的电子产品,必须采用紧凑型印刷电路板设计!换句话说,由于小印刷电路板上采用面积较大的封装,导致板上的安装空间十分有限。另外,在更小的电子产品中内置更多功能,并缩短上市时间也是至关重要的。在汽车应用中,多数印刷电路板已设计和使用多年。由于汽车应用中引入越来越多的特殊或安全功能,根据市场对于引入的新封装或不同封装的尺寸要求而频繁地重新设计是十分困难的。对于上述诸多限制和要求,“采用紧凑式 SIP 的 QFN 封装”可解决所有问题。

设计理念

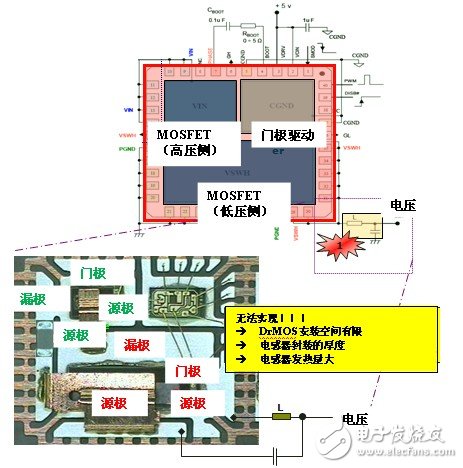

图 1 展示 DrMOS 封装中安装的无源元件。由于电子接线/引脚位置和应用,可在引脚间安装无源元件。图 2 展示无法在 DrMOS 封装中安装的电感器,无法安装的主要原因是运行时发热量大,另外电感器元件的厚度和 DrMOS 的安装空间也有影响。

图 1 DrMOS 封装中安装的无源元件

图 2 无法在 DrMOS 封装中安装的电感器

“采用紧凑式 SIP 的 QFN 封装”理念采用带有专用引脚数的预成型封装。功率产品、逻辑产品、无源元件、电阻器等可集成/安装于该预成型封装体的顶面和底面。图 3 展示“采用紧凑式 SIP 的 QFN 封装”这一新封装理念。

图 3 “采用紧凑式 SIP 的 QFN 封装”这一新封装理念封装顶面可集成驱动器芯片、MOSFET、无源元件、电感器、集成电路、WLP 甚至是逻辑芯片等,而底面则可集成 MOSFET/有源芯片或其他运行时发热量大的功率芯片。虽然 DrMOS 只是一个示例,但它可能会用于其他芯片应用。图 4 至 图 7 展示“采用紧凑式 SIP 的 QFN 封装”的不同视图。

图 4 “采用紧凑式 SIP 的 QFN 封装”的不同视图【视图 A(横截面)】

图 5 “采用紧凑式 SIP 的 QFN 封装”的不同视图【视图 B(顶面)】

图 6 “采用紧凑式 SIP 的 QFN 封装”的不同视图【视图 C/E(前面和侧面)】

图 7 “采用紧凑式 SIP 的 QFN 封装”的不同视图【视图 D(底面)】

优点:

封装设计理念

在 QFN 中集成 SIP 是全新的封装理念,具有紧凑、集成度高的特点(可集成更多的无源元件和芯片)。此设计可在内部集成具有不同功能的有源元件和无源元件,降低成本和缩短上市时间,成为最受青睐的封装技术之一。此外,该封装设计可更换不同的无源元件或芯片,从而实现不同的 BOM 组合,有助于封装产品的升级。

产品性能和应用

突破封装/产品的灵活性和可扩展性的限制

当前市场中的 SIP :在成型封装中固定和封装的无源元件、功能性芯片和 CSP 产品 à 灵活性差,在集成厚度较大的元件时需要采用新封装尺寸。对于“采用紧凑式 SIP 的 QFN 封装”设计而言:可采用多种厚度的芯片、CSP 产品、无源元件及其他功能芯片,不受限于总封装厚度。可根据客户应用或需求,以“拾取放置”(pick & place) 方式更换无源元件、CSP 产品及其他功能芯片。由于采用暴露元件/“开放式”封装理念,对于芯片、CSP 产品、无源元件或其他功能芯片无严格厚度限制。开发工作量少,上市时间短,封装灵活性高。

工艺简化

由于采用的是倒装芯片设计,封装时无需采用焊线和成型工艺。总体而言,这将极大地简化整体工艺。

可靠性高

由于采用了预成型引脚框,且其为“开放式”,因此无需担心成型复合物和无源元件/硅芯片表面之间的 CTE (热膨胀系数)不匹配问题。无源元件和引脚框之间的间隙极小,不存在封装气孔的问题。无源元件与引脚框之间(如 I/O 区域)的细小间隙通常会导致形成微小气孔。在压力测试过程中,孔内的空气可能会导致“爆米花”效应。热性能增强

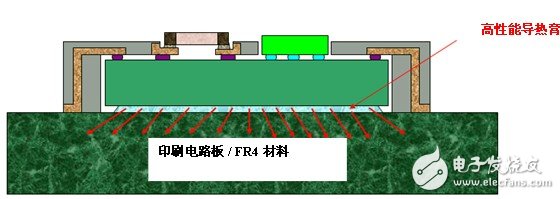

对于高发热量芯片应用,可在有源芯片的背面涂覆额外的高性能导热膏,从而增强热性能。热量传导路径为:有源芯片 à 高性能导热膏 à 印刷电路板

以下说明“采用紧凑式 SIP 的 QFN 封装”封装设计与市场中现有的 SIP 封装的细小差异。

图 8 “采用紧凑式 SIP 的 QFN 封装”封装设计与市场中现有的 SIP 封装的细小差异

采用紧凑式 SIP 的 QFN 封装:

+ 突破灵活性和封装/产品可扩展性的限制 à 可使用更大、更厚的无源元件尺寸,利于扩展产品和改善性能。

+ 产品性能和应用 à 无源元件能够尽可能地靠近有源芯片进行安装,从而获得最佳的产品性能。例如,DrMOS 要求元件尽可能地靠近 HS 芯片的漏极和 LS 芯片的源极。

+ 上市时间 à 可快速制造出产品扩展或使用更厚元件的样品

+ 可靠性 à 未采用复合物成型封装,避免无源元件与引脚框之间形成封装气孔类似于印刷电路板上的无源元件

图 9 采用紧凑式 SIP 的 QFN 封装

市场中现有的 SIP:

– 封装/产品的灵活性和可扩展性差 à 受限于封装厚度,无法使用较大、较厚的无源元件,不适于产品扩展。

– 导电路径较长,电阻较大。信号传输质量/效率必然因此受到影响。

– 由于需要构建新封装平台和引进成型模具,上市时间较长。

– 可靠性 à 由于无源元件与引脚框表面间的间隙会导致形成封装气孔,在压力测试过程中可能存在“爆米花”效应风险。

对于高发热量芯片应用,可在有源芯片的背面涂覆额外的高性能导热膏,从而增强热性能(图 10)。

图 10 对于高发热量芯片应用,可在有源芯片的背面涂覆额外的高性能导热膏,从而增强热性能

工艺流程:

“采用紧凑式 SIP 的 QFN 封装”可简化装配工艺。下图展示装配工艺流程的诸多概念之一(图 11)。

图 11装配工艺流程的诸多概念之一图示

工艺流程描述:

A – B 有源芯片通过锡球焊接、丝网印刷、印刷电路板装配 (PCBA) 或其他市场中现有的布线工艺安装于预成型引脚框中。

B – C ‘A – B’ 中所述的预成型引脚框随后进行 180 度翻转以便将其他芯片、WLP、IC 产品或其他元件安装到有源芯片表面上的 I/O 叉状物。

D: 无源元件或其他半导体封装随后将通过锡球焊接、丝网印刷、印刷电路板装配 (PCBA) 或其他市场中现有的布线工艺安装于预成型引脚框中。封装(框式)将被送至下一流程,例如封装切割、测试、印制标记和包装。

![]()