在谈到Universal Curve时,我们提到对于MOS器件性能的追求,简而言之就是更大的Ion和更小的Ioff,换句话讲就是“开源节流”。为了实现更小的Ioff,就要尽可能地堵住漏电通路,我们之前已经谈过了DIBL和GIDL,今天要讲的Source Drain Punch Through是另一个重要的漏电通道。

鲁迅先生告诉我们,在PN结交界的地方会存在空间电荷区,或者叫耗尽区。耗尽区宽度会随着PN结反偏电压的增大而扩展。一般而言,耗尽区的宽度从几十纳米到微米不等,取决于掺杂浓度等因素。对于长沟道器件,沟道长度在几微米甚至更大,那么源漏区的耗尽区各自安好,但是随着沟道长度变短,两边的耗尽区会越来越近,甚至会靠在一起。这个时候便是所谓的源漏的耗尽区穿通,英文名曰Punch Through,由于这种穿通发生在沟道区之外的Bulk区,所以也可以叫Bulk Punch Through。

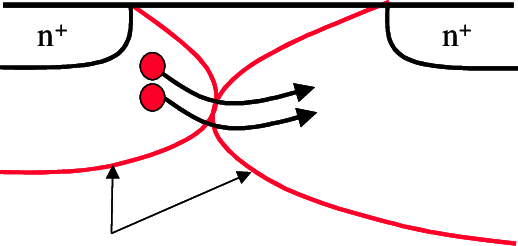

Punch through示意图。引自Dragica Vasileska et al. “Tutorial for PADRE-Based SimulaTIon Modules (PN JuncTIon Lab, MOSCap Lab, BJT Lab, MOSFET Lab, MESFET Lab)”

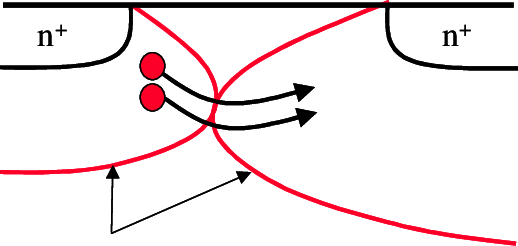

以NMOS为例在源漏穿通发生之后,对于载流子而言存在一个N-D-N的通道。源极的部分电子进入耗尽区后,有一定可能被电场直接扫进漏极,进而被漏极收集,从而实现电流从源极到漏极的导通。这个电流被称为耗尽区限制的电流,其值大约呈以下关系:

其中A是punch through区域的面积,L是沟道长度。

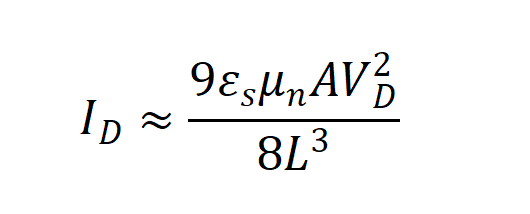

下图是不同沟道长度器件(1.5微米、3微米、7微米)在不同Vd下的亚阈值电流行为。此处便是DIBL与Punch through的联合演出。在7微米器件下,几乎看不到短沟道效应,即在不同Vd下的曲线几乎重合。而到3微米器件中,已经有明显的短沟道效应,在大的Vd下,Swing已经开始恶化。而1.5微米的器件,此时已经发生了严重的短沟道效应,转移特性曲线在亚阈值区已经几乎变成一条直线,这意味着已经无法关断,完全丧失了功能。

0.23微米器件的亚阈值特性。引自S.M.Sze“Semiconductor Devices Physics and Technology”

![]()