追溯芯片封装历史,将单个单元从整个晶圆中切割下来再进行后续封装测试的方式一直以来都是半导体芯片制造的“规定模式”。然而,随着芯片制造成本的飞速提升以及消费市场对于芯片性能的不断追求,人们开始意识到革新先进封装技术的必要性,因此, 晶圆级封装诞生了。

晶圆级封装(Wafer Level Packaging,缩写WLP)是一种先进的封装技术,因其具有尺寸小、电性能优良、散热好、成本低等优势,近年来发展迅速。根据Verified Market Research 研究数据,晶圆级封装市场 2020 年为 48.4 亿美元,预计到 2028 年将达到 228.3 亿美元,从 2021 年到2028 年的复合年增长率为 21.4%。

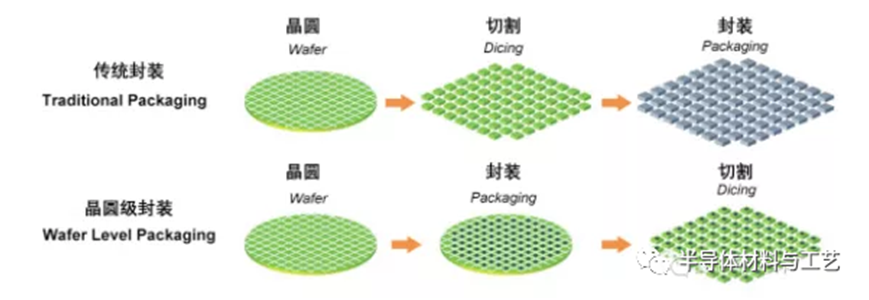

不同于传统封装工艺,晶圆级封装是在芯片还在晶圆上的时候就对芯片进行封装,保护层可以黏接在晶圆的顶部或底部,然后连接电路,再将晶圆切成单个芯片。

晶圆级封装技术与打线型(Wire-Bond)和倒装型(Flip-Chip)封装技术相比 ,能省去打金属线、外延引脚(如QFP)、基板或引线框等工序,所以具备封装尺寸小、电气性能好的优势。

封装行业的领跑者们大多基于晶圆模式来批量生产先进晶圆级封装产品,不但可利用现有的晶圆级制造设备来完成主体封装制程的操作,而且让封装结构、芯片布局的设计并行成为现实,进而显著缩短了设计和生产周期,降低了整体项目成本。

相比于传统封装,晶圆级封装具有以下优点:

1、封装尺寸小

由于没有引线、键合和塑胶工艺,封装无需向芯片外扩展,使得WLP的封装尺寸几乎等于芯片尺寸。

2、高传输速度

与传统金属引线产品相比,WLP一般有较短的连接线路,在高效能要求如高频下,会有较好的表现。

3、高密度连接

WLP可运用数组式连接,芯片和电路板之间连接不限制于芯片四周,提高单位面积的连接密度。

4、生产周期短

WLP从芯片制造到、封装到成品的整个过程中,中间环节大大减少,生产效率高,周期缩短很多。

5、工艺成本低

WLP是在硅片层面上完成封装测试的,以批量化的生产方式达到成本最小化的目标。WLP的成本取决于每个硅片上合格芯片的数量,芯片设计尺寸减小和硅片尺寸增大的发展趋势使得单个器件封装的成本相应地减少。WLP可充分利用晶圆制造设备,生产设施费用低。

需要强调的一点是,与打线型封装技术不同,用晶圆级封装用晶圆级封装技术来实现腔内信号布线(Internal Signal Routing),有多个选项:晶圆级凸块(Wafer Bumping)技术、再分布层(Re-Distribution Layer)技术、硅介层(Silicon Interposer)技术、硅穿孔(Through Silicon Via)技术等。

先进晶圆级封装技术,主要包括了五大要素:

①晶圆级凸块(Wafer Bumping)技术;

②扇入型(Fan-In)晶圆级封装技术;

③扇出型(Fan-Out)晶圆级封装技术;

④2.5D 晶圆级封装技术(包含IPD);

⑤3D 晶圆级封装技术(包含IPD)。

晶圆凸块(Wafer Bumping),顾名思义,即是在切割晶圆之前,于晶圆的预设位置上形成或安装焊球(亦称凸块)。晶圆凸块是实现芯片与 PCB 或基板(Substrate)互连的关键技术。凸块的选材、构造、尺寸设计,受多种因素影响,如封装大小、成本及电气、机械、散热等性能要求。

印刷型凸点(Printed Bump)技术、共晶电镀型落球(Ball Drop with Eutectic Plating)技术、无铅合金(Lead-Free Alloy)及铜支柱合金(Copper-Pillar Alloy)凸点技术,扇入型晶圆级封装(Fan-In Wafer Level Package,FIWLP)技术,业内亦称晶圆级芯片规模封装(Wafer Level Chip Scale Package,WLCSP)技术,是当今各类晶圆级封装技术中的主力。近两年,扇入型晶圆级封装产品的全球出货量都保持在每年三百亿颗以上,主要供给手机、智能穿戴等便携型电子产品市场。

随着便携型电子产品的空间不断缩小、工作频率日益升高及功能需求的多样化,芯片输入/输出(I/O)信号接口的数目大幅增加,凸块及焊球间距(Bump Pitch & Ball Pitch)的精密程度要求渐趋严格,再分布层(RDL)技术的量产良率也因此越发受重视。在这种背景下,扇出型封装(Fan-Out Wafer Level Package,FOWLP) 及扇入扇出混合型(Hybrid Fan-In/Fan-Out)等高端晶圆级封装技术应运而生。

这里我们拓展介绍一下,再分布层(Re-Distribution Layer,RDL)技术。在晶圆级封装制程里面, 再分布层技术主要用于在裸芯(Bare Die)和焊球之间重新规划(也可理解为优化)信号布线、传输的路径,以达到将晶圆级封装产品的信号互联密度、整体灵活度最大化的目的。RDL 的技术核心,简单来说就是在原本的晶圆上附加了一层或多层的横向连接,用来传输信号。

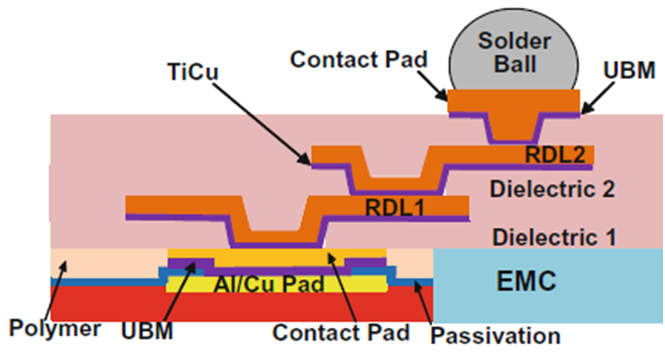

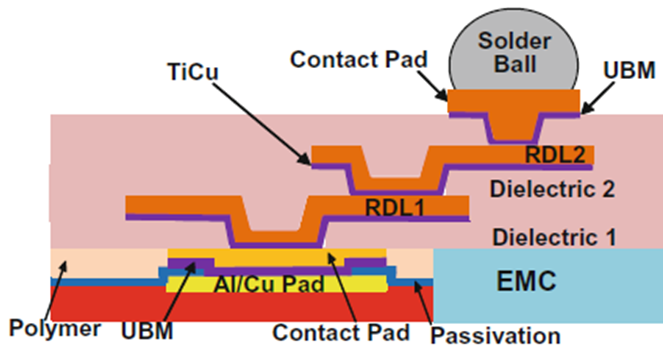

下图所示为典型的 Chip-First RDL 方案。请注意在这里有两层电介质(Dielectric)材料,用来保护被其包裹的 RDL 层(可理解为应力缓冲)。另外,凸块冶金(Under Bump Metallurgy,UBM)技术在这里也派上了用场,来帮助触点(Contact Pad)支撑焊球、RDL 还有电介质。

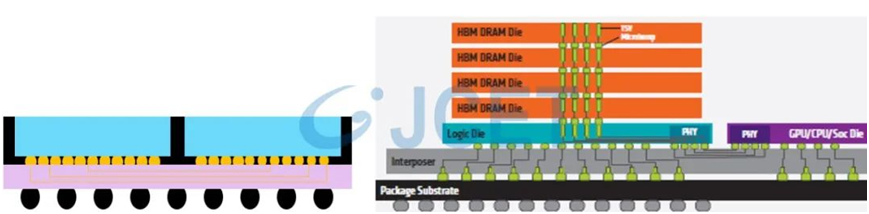

随着超高密度多芯片模组(Multiple Chip Module,MCM)乃至系统级封装(SiP)产品在5G、AI、高性能运算、汽车自动驾驶等领域的普及,2.5D 和 3D 晶圆级封装技术备受设计人员青睐。下图所示为 2.5D(左)和 3D(右)晶圆级封装技术。

如上方图左所示,对 2.5D 晶圆级封装技术而言,两颗芯片的信号互联,可以通过再分布层(Re-Distribution Layer,RDL)或者硅介层(Silicon Interposer)技术来实现,如上方图右所示,对 3D 晶圆级封装技术而言,逻辑、通讯类芯片如 CPU、GPU、ASIC、PHY 的信号互联,也可通过再分布层(RDL)或硅介层(Silicon Interposer)技术来实现。但是,3D 堆叠起来的多个高带宽存储(High-Bandwidth Memory,HBM)芯片与其底部的逻辑类芯片的信号互联,则由硅穿孔(Through Silicon Via,TSV)技术来实现。当然,以上几种互联(Interconnect)如何取舍,需按实际规格、成本目标做 case-by-case 分析。

不论着眼现在,还是放眼未来,随着 5G、人工智能、物联网等大技术趋势奔涌而至,在高密度异构集成的技术竞赛中,晶圆级封装技术必将占有一席之地。

(文章来源:深圳市赛姆烯金科技有限公司)

![]()