世界上所有的制造业都是建立在堆叠具有各种公差和变化范围的多个过程和系统之上的,以获得始终如一的有用产品。这一点在半导体制造中表现得最为明显,因为它是世界上最复杂的制造工艺,对错误的容忍度最低。尽管存在这些挑战,半导体行业还是将数百个抽象层堆叠在一起,以便软件世界看到一个一致的设备。当层被剥离时,极大的变化就会显现出来。

从晶圆厂出来的每个芯片,即使是相同的设计,对于任何给定的性能水平也会消耗不同的功率。许多芯片都会有缺陷,导致最终芯片在几个禁用的“内核”和 IO 的情况下收获良率。例如,所有 Nvidia A100 和 H100 GPU 都禁用了约 10% 的芯片。原因在于现代高性能半导体上数十亿个晶体管和互连中嵌入的制造差异,这些差异是通过数千个不同的工艺步骤创建的。每个单独的晶体管将需要不同量的电压来切换。互连、过孔和接触的每一部分将具有不同的电阻。

让我们看看 EUV 光刻,因为这是制造先进半导体的核心技术之一。其全流程涉及了从 EUV 光源到反射镜系统,再到光掩模,再到对准系统,再到晶圆载物台,再到光刻胶化学成分,再到镀膜机和显影剂,再到计量学,再到单个晶圆。

EUV 是一个充满复杂性、不确定性和不完美的过程,但它确实有效。台积电、三星和 SK 海力士都在生产不同数量的 EUV。英特尔还秘密表示,他们正在为intel 4 工艺节点中的 EUV 光刻做好制造准备。我们并不真的相信他们,因为我们获得的内部文件显示英特尔首款使用 EUV 的大批量产品 Meteor Lake 再次被推迟,“准备发货”日期至少推迟到 2023 年第 52 周。这表明英特尔在将生产规模设计实施到 EUV 工艺技术方面面临挑战。

单个过程步骤中的微小变化累积起来可能会严重偏离预期结果,最终导致最终产品失败。例如,飞机发动机中的激光钻孔或精密铸造问题可能导致涡轮叶片不平衡。这种不平衡的涡轮机将导致额外的振动,降低效率并最终导致发动机磨损并提前失效。现在考虑一下,飞机发动机在制造精度、工艺变化公差范围、化学、物理和步骤数量方面比半导体简单得多。

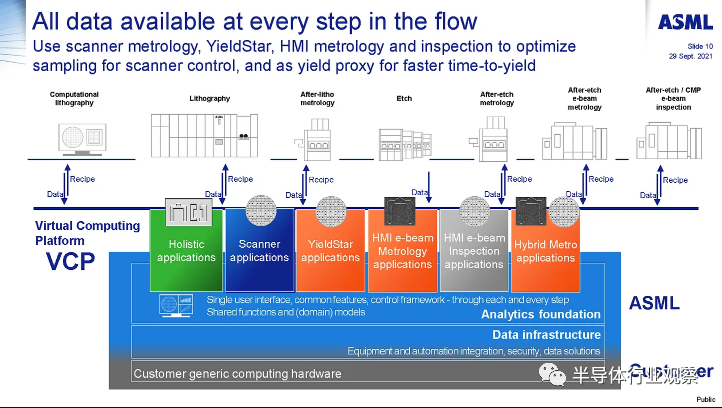

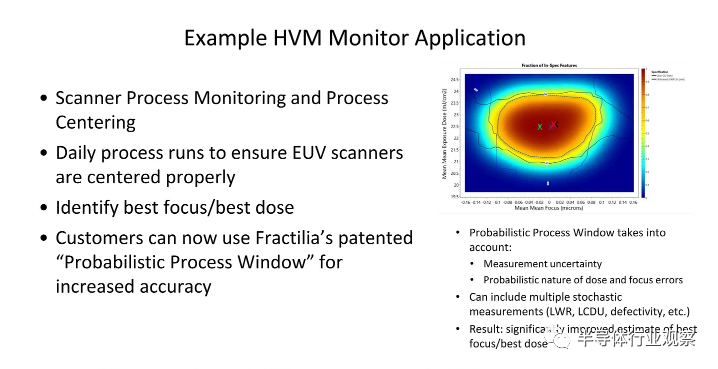

前沿晶圆厂中的大多数工具都可以在几个原子的精度内沉积、抛光或蚀刻材料。数千个工具/流程步骤链中的每个后续工具都将不断调整其流程参数。这些条件和调整是通过使用过程控制来确定的。过程控制包括计量/检测工具和控制它的软件。晶圆厂每年在过程控制上的花费超过 200 亿美元。

如果蚀刻工具有四个腔室,过程控制智能和晶圆厂网络路由将根据该工艺步骤中的可用性和产量指标来确定将晶圆发送到四个腔室中的哪一个。他们还将调整腔室条件并监控是否需要维护。事实上,即使是落后的晶圆厂也会为每个单独的晶圆或批次调整工具设置,以将每个特征的累积公差范围保持在最低可行规格。

为了强调这一点,高度的变化和不确定性是如此普遍,以至于生产晶圆厂将使用多种不同的 EUV 工具测试光掩模。这些生产工厂可能只在一种特定的 EUV 工具上运行该光掩模,以产生最高的产量或最可控的缺陷。请注意,现代台积电 5nm 设计有约 81 个掩模,单个晶圆厂每年将运行数十或数百个设计。此外,光掩模与 EUV 工具的匹配会定期重新测试,因为掩模必须半定期地进行维修或重制。

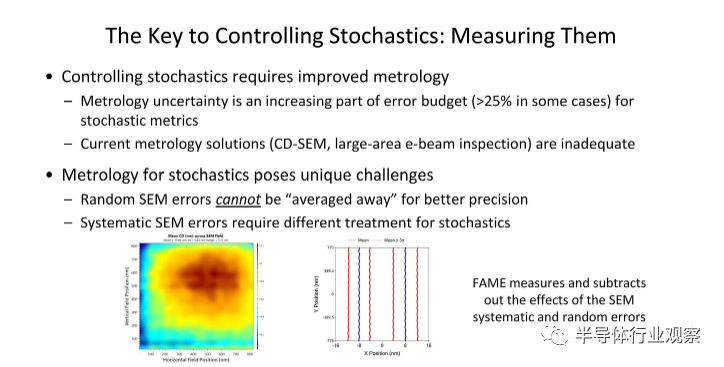

类似地,即使相同类型的计量/检测工具是从同一设施创建和运输的,它们也可能只用于选定的层,因为在测量只有几个原子的特征时,工具与工具之间的差异很大在尺寸方面。事实上,在某些情况下,超过 25% 的误差预算(堆叠变化)被计量和检测成像工具的不确定性所消耗。旨在提供数据以帮助调整使用中的工具和流程的工具也非常不完美。

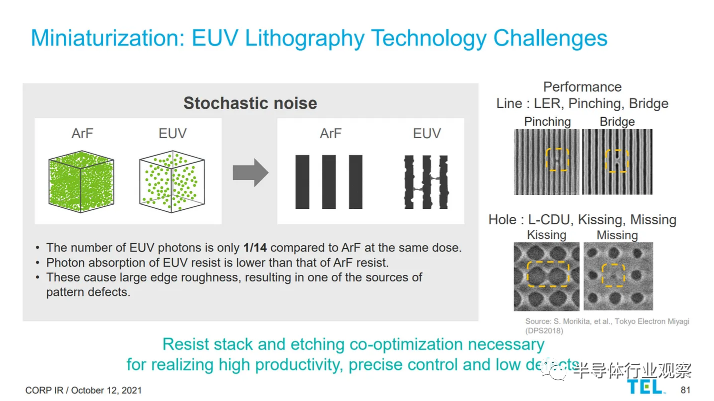

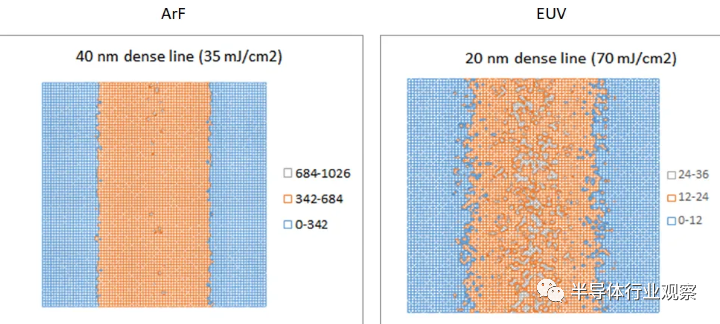

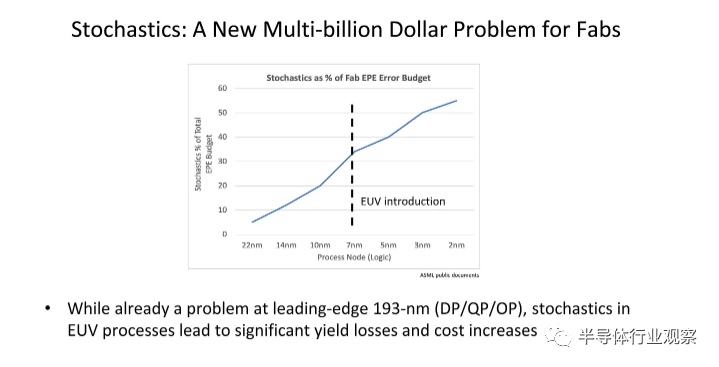

晶圆厂必须跳过很多很多的漏洞,才能相信他们的计量设备能够准确描述他们正在处理的晶圆上实际发生的情况。许多错误和缺陷源于 EUV 工具和工艺。在相同剂量下,相对于 DUV ,EUV仅仅有 1/14 的光子撞击晶圆。因此,这引入了相当多的随机缺陷,这些缺陷源于更少光子的更随机分布。EUV 光刻中的随机性是指图案中可能发生的随机变化。

这些随机缺陷对晶圆制造行业来说是一个价值数十亿美元的问题。数百亿美元用于表征计量和检测工具的变化。然后将此处生成的数据反馈到逐个晶圆、逐个设计或逐个工具的修改过程或工具参数中。没有两个晶圆、工具或设计是相同的,并且在晶圆厂网络的每个方面都有大量的调整和优化。

一个 gigafab 将在约 250,000 个飞行中的晶圆上运行 1000 个步骤,其中约 100,000 个在一个月内完成,新的 100,000 个在一个月内开始。不能低估路由、优化和决策的后勤挑战。

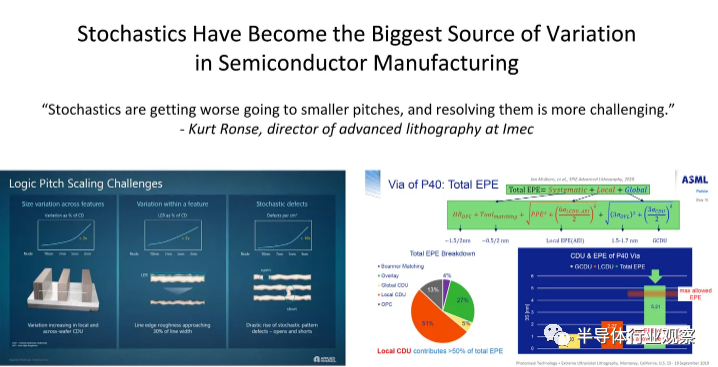

因为在这过程中,随机指标不仅呈线性增长,而且它们在我们打印的关键维度中所占的百分比呈指数增长。

我们有机会与 Chris Mack(又名“Litho Guru”)聊了聊该行业面临的许多困难以及已经开发的一些解决方案。对于那些不知道的人,Chris Mack 曾与 Lotus Elise 打赌 EUV 不会在 SPIE 光刻和高级图案会议的特定日期前准备好。另一个有趣的故事是,他在这次会议上开玩笑地制作并戴了一顶红色的“Make EUV Great Again”帽子。

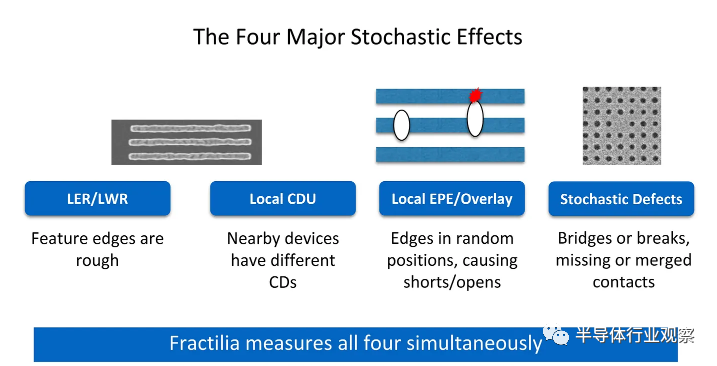

有一些主要的变化和缺陷类别。这些都会增加导线电阻、栅极泄漏,甚至导致短路或其他导致芯片无法使用的缺陷。

叠加/局部边缘放置错误

如前所述,台积电 5nm 工艺有约 81 个光掩模。这是经历整个光刻过程的 81 个不同实例。此外,中间还会有数以千计的其他制造步骤。

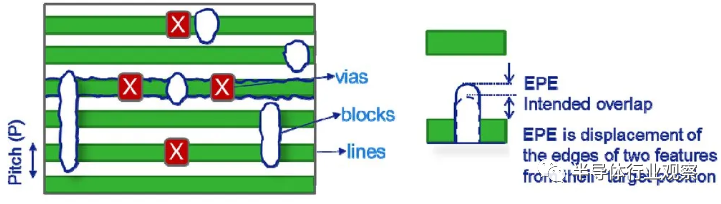

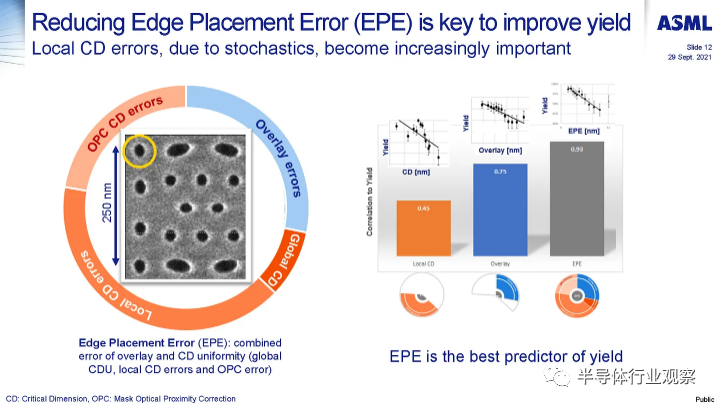

覆盖或局部边缘放置错误是沉积、光刻、蚀刻循环中的一个特征放置在前一个循环中的另一个特征之上的变化。一层上的 +1nm 未对准和下一层上的 -1nm 未对准在特征放置方面的差异最多可达 2nm。这些类型的错误可能会在许多步骤中累积起来,并且可能是灾难性的。

我们在曾经讨论的一个例子是 TSMC 与 Intel 的自对准触点,它们试图通过使图案化特征更能抵抗放置错误来减轻一些叠加错误的堆叠。

局部临界尺寸均匀性 (CDU)

变化的另一个主要来源是局部临界尺寸均匀性。如果我们希望彼此相邻的特征理想情况下应该是统一的,但在许多情况下,它们不是。在这个例子中,让我们缩小到连接芯片各个金属层的过孔和触点。

当这些随机变化变得足够大时,它们会导致缺陷丢失或合并:接触极、桥接、断裂、线路和空间。如果你的芯片上有 1000 亿个触点/通孔,其中一个丢失了,那么你的整个芯片就坏了(当然会内置一些冗余)。对于直径仅为几十纳米的特征,该行业的缺陷率必须约为千亿分之一。

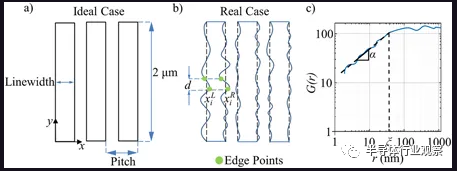

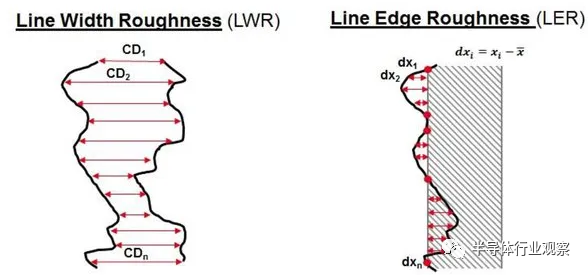

线边缘粗糙度 (LER)

线边缘粗糙度 (LER) 是特征边缘的变化。LER 可以定义为图形特征边缘的粗糙度或不规则性,例如线条或沟槽,这可能导致偏离所需的关键尺寸。

LER 会对最终产品的性能和可靠性产生重大影响。例如,在晶体管栅极的情况下,LER 的变化会影响晶体管的电气特性,从而导致漏电流增加和器件性能降低等问题。

线宽粗糙度 (LWR)

LWR 可以定义为特征宽度的粗糙度或不规则性,例如线条或沟槽,这会导致偏离所需的临界尺寸。在金属互连的情况下,LWR 的变化会影响线路的电阻,从而导致功耗增加或设备性能降低等问题。

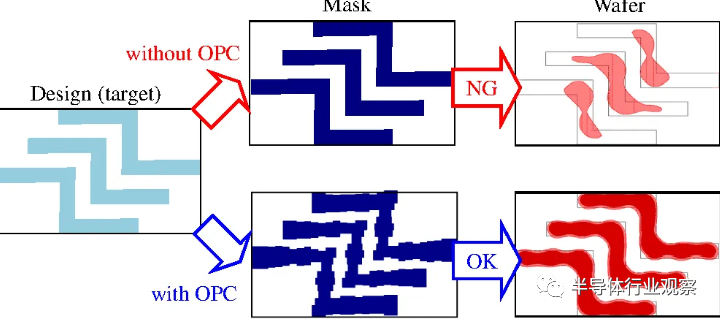

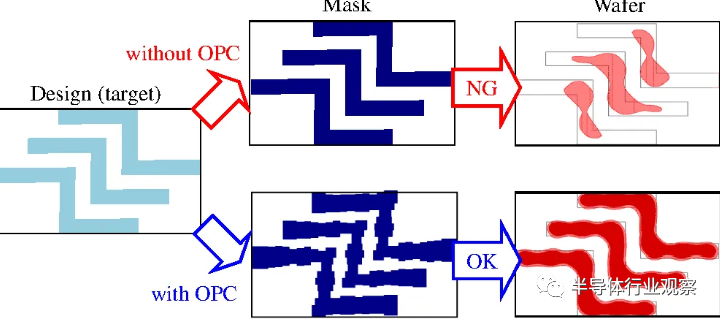

光学邻近校正 (OPC)

光掩模可以被认为是芯片的模板。光掩模用电子束图案化并放置在光刻工具内。然后,光掩模可以吸收或散射光子,或允许它们穿过晶圆。这就是在晶圆上创建图案的原因。

OPC 旨在纠正光刻过程中发生的图案化特征的扭曲或变形。通过对它们进行补偿,制造商可以在图形特征中实现更高的准确性和一致性,从而提高最终产品的性能和可靠性。下面是具有更高级条件的 OPC 的早期形式,包括在 TSMC 批量使用曲线 ILT 掩模。

(文章来源:semianalysis编译)

![]()