2022年,集成电路半导体行业最热的头条是“EDA被全面封锁”。如何突破EDA封锁,成为行业发展的关键词,也是群体焦虑。在全球市场,有人比喻EDA是“芯片之母”,如果没有了芯片,工业发展和社会进步将处处受制,EDA的重要性也上升到了战略性高度。尽管国际封锁形势严峻,但睿智的中国科技人擅于把危机化为机会,从《加快自主研发应用,让工业软件不再卡脖子》,到《破解科技卡脖子要打好三张牌》,即一要打好“基础牌”,提升基础创新能力;二要打好“应用牌”,加强对高精尖国货的应用;三是要打好“人才牌”,让人才留得住、用得上、有发展……,各种政策、举措和实际行动,处处彰显了我们中国科技的发展韧性。

我们EDA探索频道,今天迎来了第12期的内容——MOSFET收缩(2)- Heterogeneous Era,下面就跟着小编一起来开启今天的探索之旅吧~

上一期我们谈到了芯片的微缩规则,在微米时代,基本上依据这个规则就可以实现集成电路的微缩,所以称为“Happy Scaling Era”。然而,当集成电路发现到深亚微米,尤其在90nm这一代时,就Happy不起来了。比如,SiO2栅氧化物被缩小到约1.2纳米时,栅氧化物的漏电流呈指数增加。传统的MOSFET缩放规则也要求电源电压的缩小(尽管不是完全按比例的),降低供应电压和阈值电压会导致越来越高的亚阈值漏电流。如果不能对栅氧化物厚度和阈值电压进行缩放,传统的微缩规则就没有办法正常地工作了。

简单的微缩规则又称为同质(homogenous)微缩,意即器件的物理结构不发生大的改变,各种关键的几何尺寸同时发生收缩。当同质微缩没有办法满足集成电路的发展时,自然就进入了异质(heterogenous)微缩的时间。所谓异质,即在器件的材料和结构上出现了较大的变化,新物理机制的引入大大增强了器件的性能,从而推动摩尔定律的持续发展。

一般来说,在器件层面最关键的改进有四项,应力工程,高介电常数介质/金属栅,绝缘体上硅和FinFET。

应力工程

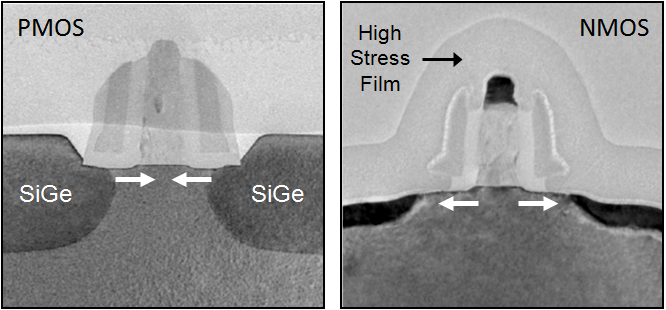

在Intel的90nm技术节点,栅氧化层厚度被压缩到了约1.2nm,相比于0.13微米仅缩小了大约0.8倍,从所周知,继续微缩规划,新的一代技术要达到0.7倍的尺寸才能满足需求。而由于不可抑制的隧道效应,栅氧不可能降低。Intel在PMOS引入了锗硅材料,来对沟道施加压应力,在NMOS引入氧化硅的应力层,来对沟道施加张应力。由于应力的引入,增强了载流子的迁移率。从而补足了栅氧化层微缩不够的性能损失。而在65nm技术节点,栅氧化层没有微缩,通过应力工程的进一步加强,实现了器件性能的提升。代工厂方面,台积电在45/40这一代技术节点也全面采用了应力工程来提升器件性能。

图:Intel 90nm节点PMOS与NMOS截面图。引自Mark Bohr,The Evolution of Scaling from the Homogeneous Era to the Heterogeneous Era, IEDM 2011

HKMG

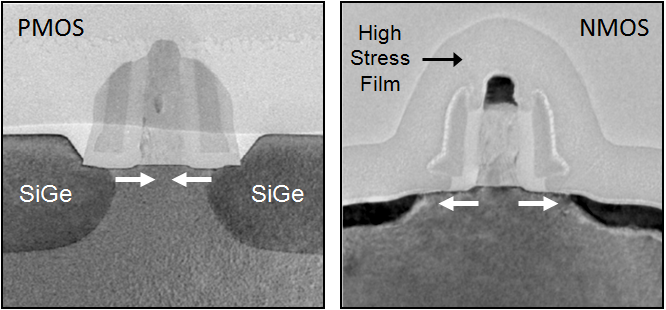

应力工程可以在栅氧不微缩的情况下推动两代技术进步,然而栅极本身的限制也是不得不面对的问题。为了增强器件性能,我们需要栅极有尽量厚的物理厚度,以抑制漏电流的产生,同时还要有尽量薄的等效厚度,以使栅电压有效地作用在沟道上。这就指向了必须找到高介电常数(High K)的绝缘材料,来同时满足两个方面的要求。到了Intel的45nm时代,氧化铪被选中成为新的栅氧化层材料。

图:Intel的HighK技术宣传材料

与之相配套的,栅极材料由多晶硅换回了金属材料(早期的栅极材料是铝,其后改为多晶硅以实现自对准工艺),以应对多晶硅耗尽引起的电阻增大等问题。从而增强了驱动能力和器件性能的均匀性。

High K材料与金属栅实际上是两项技术改进,但是由于他们往往联袂出现,所以经常称为HKMG。

图:Intel的器件性能进步。引自Mark Bohr,The Evolution of Scaling from the Homogeneous Era to the Heterogeneous Era, IEDM 2011

HMKG技术帮助Intel继续将技术推进至45nm和32nm两代,台积电等代工厂在28nm技术节点也全面引入HKMG。至此,应力工程结合HKMG,以及Silicide,Low K层间介质等技术将集成电路的平面工艺推至巅峰。单个器件的性能达到了之前无法想象的水平,同时也越来越逼近物理上的极限。为了推动集成度的进一步提升,集成电路产业从二维平面飞升到了三维。

(文章来源:鸿之微)

![]()