为什么要从FinFET转向纳米片?

按照逻辑CMOS的发展路径,业界为逐步减少逻辑标准单元库的尺寸做出了相当大的努力。

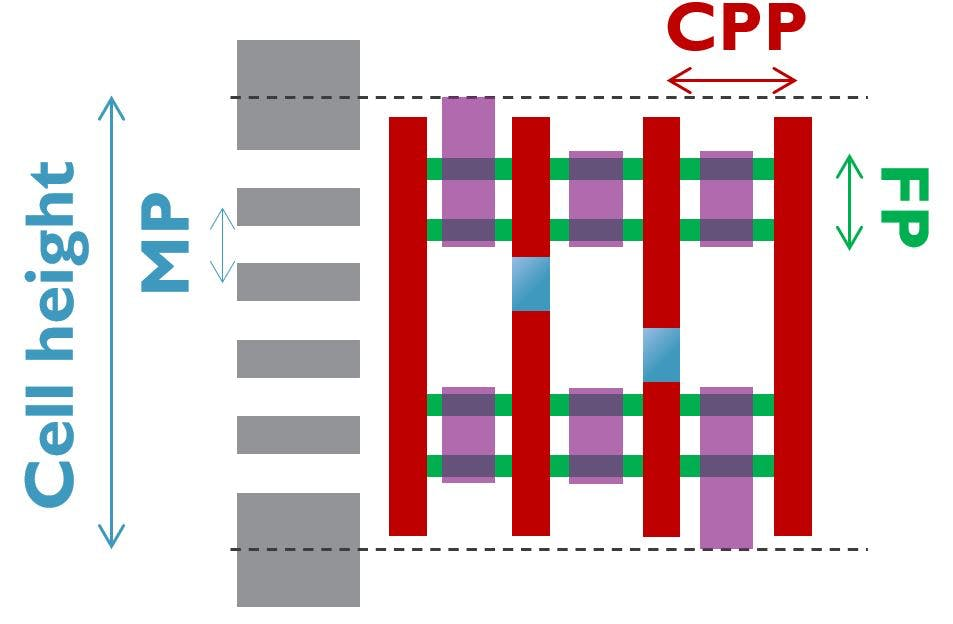

逻辑标准单元布局的示意图(CPP=接触的多孔间距,FP=Fin间距,MP=金属间距;单元高度=每单元的金属线数xMP)。

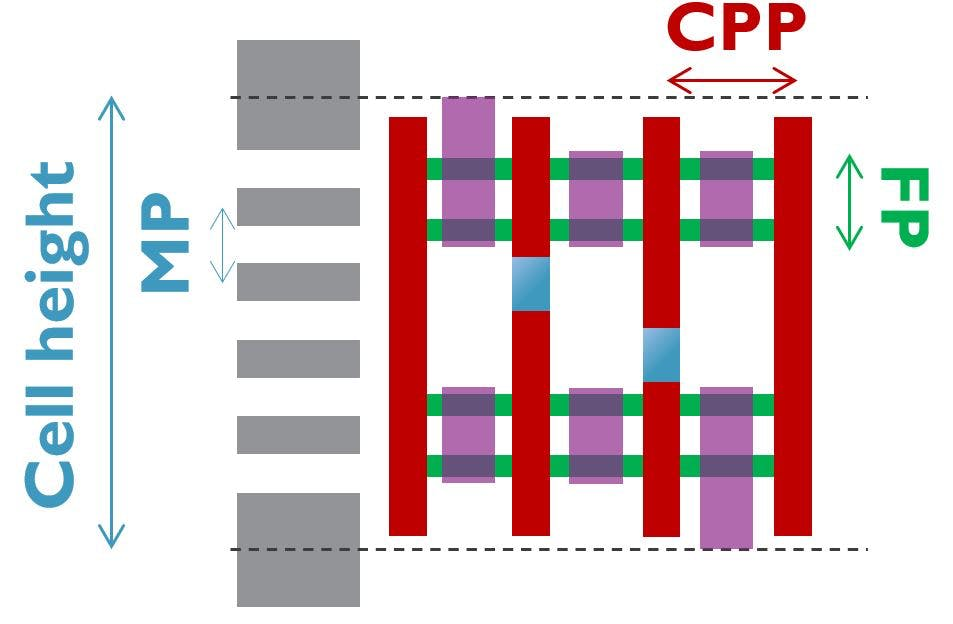

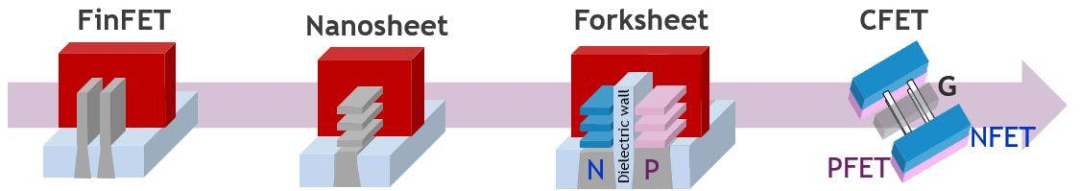

做到这一点的一个方法是通过减少轨道数来降低单元高度–它被定义为每个单元的金属线(或轨道)的数量乘以金属间距。对于FinFET,通过逐步将一个标准单元内的Fin数量从3个减少到2个,实现了具有更小的单元高度的新一代产品,如7.5T和6T标准单元。然而,如果保持Fin的尺寸,这种变化是以牺牲驱动电流和变异性为代价的。为了补偿驱动电流和变异性的退化,在单元高度的缩放中,Fin越来越高。最终可以持续到1个Fin,并且可以实现5T标准单元。

在基于FinFET的架构中,为了实现标准单元的减小,需要减小Fin的数量。Fin越来越高、越来越薄、越来越近。这种演变降低了驱动强度,增加了变异性。

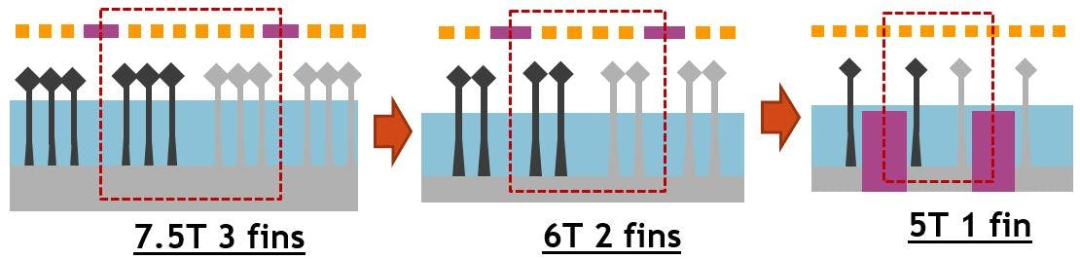

然而,进一步提高基于5T FinFET的单Fin器件架构的驱动电流是极具挑战性的。而这正是纳米片架构可以解决问题的地方。通过在只允许一个Fin的标准单元中垂直堆叠纳米片状的传导通道,可以实现更大的有效沟道宽度。这样,纳米片可以提供比Fin更大的单位面积驱动电流–这是进一步扩大CMOS规模的关键优势。纳米片结构还允许可变的器件宽度,这使得设计具有一定的灵活性:设计者可以通过减少面积和电容来得到增强的驱动电流(较小的沟道宽度倾向于减少片间的寄生电容)。与FinFET架构相比,纳米片的另一个显著优势是它的 “全栅极 “结构:由于传导通道现在完全被HKMG所包围,对于较短的沟道长度,可以实现对沟道更好的栅极控制。

垂直堆叠的GAA(Gate All Around)纳米片晶体管的优化。(左)纳米片形状控制;(右)纳米片垂直空间分隔的减小。

Forksheet

进一步提高直流性能最优雅的方法是扩大沟道的有效宽度。但在传统的纳米片结构中,这变得非常困难。主要的障碍在于n型和p型器件之间需要很大的空间余量,这使得有效纳米片宽度在按比例的单元高度中变得困难,空间被功函数金属的图形化步骤所消耗。Forksheet器件结构可以解决这一挑战。Forksheet是imec在2017年(IEDM 2017)首次公开提出用于SRAM微缩,后来(IEDM 2019)又用作逻辑标准单元微缩。在这种架构中,通过在栅极图案化之前在n-和pMOS器件之间引入一个电介质墙,实现了更小的n-p分离。功函数金属图案的遮蔽图案现在可以在介质壁上完成,而不像在纳米片的制造中在的栅极的底部。这使得n-p间距更加紧密。

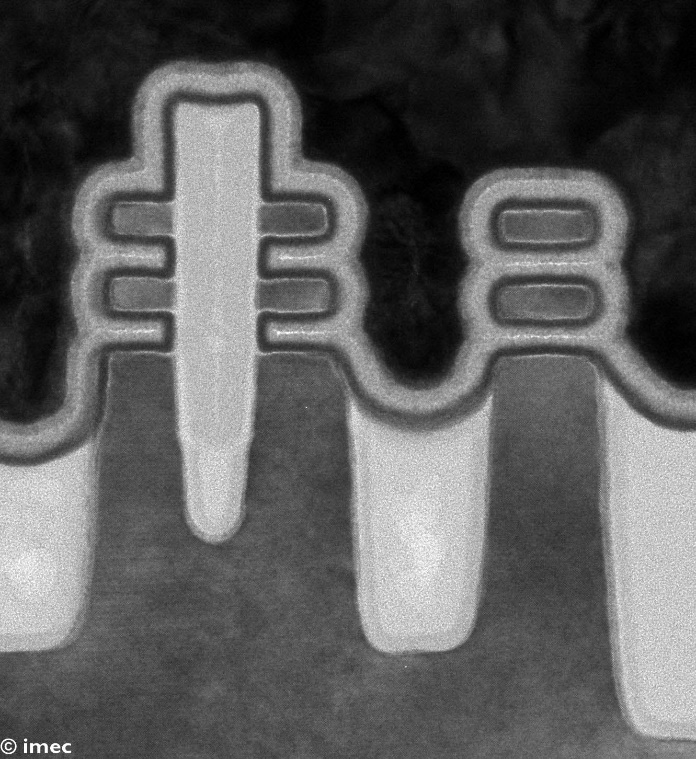

制备在一起的Forksheet和纳米片器件管的TEM照片。对于Forksheet,n和p器件管的间距是17nm

CFET

有效沟道宽度的进一步扩大是通过互补FET(或CFET)结构实现的,其中n-和pMOS器件相互堆叠在一起。这将n-p分隔转移到了垂直方向,因此从单元高度的考虑中去除n-p间距。沟道宽度可以进一步扩大,由此产生的面积增益也可用于将轨道高度推至4T及以下。仿真表明,CFET对未来的逻辑以及SRAM的面积微缩都是有帮助的。在CFET中,沟道可以以Fin(p-Fin上的n-Fin)或纳米片(p-片上的n-片)的形式制成。

从Finfet到CFET

从工艺的角度来看,制造CFET是相当复杂的。有不同的制备路线,目前仍在探索中。

结论

我们回顾了为CMOS逻辑器件微缩引入纳米片式晶体管架构的主要好处和挑战。每一代新产品——由纳米片、Forksheet和CFET实现——都伴随着性能的提高(通过优化有效沟道宽度)和逻辑标准单元高度的进一步降低。从工艺的角度来看,纳米片架构可以被认为是FinFET架构的一个进化步骤。然而,每一种不同的纳米片架构都伴随着特定的集成挑战,对此,IMEC将继续探索和评估解决方案。

(文章来源:鸿之微)

![]()