1

半导体芯片热痛点介绍

半导体技术按摩尔定理的发展,集成电路的密度将越来越高,且尺寸越来越小。所有芯片工作时都会发热,热量的累积必导致结点温度的升高,随着结点温度提高,半导体元器件性能将会下降,甚至造成损害。因此每个芯片厂家都会规定其半导元体器件的最大结点温度。

如今,在高速的集成电路中,芯片的功耗大,在自然条件下的散热已不能保证芯片的结点温度不超过允许工作温度,因此就需要考虑芯片的散热问题。为了保证元器件的结温低于最大允许温度,经由封装进行的从 IC 自身到周围环境的有效散热就至关重要。

2

案例提要

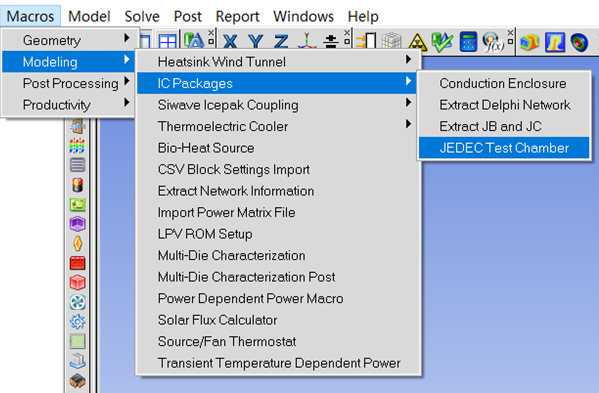

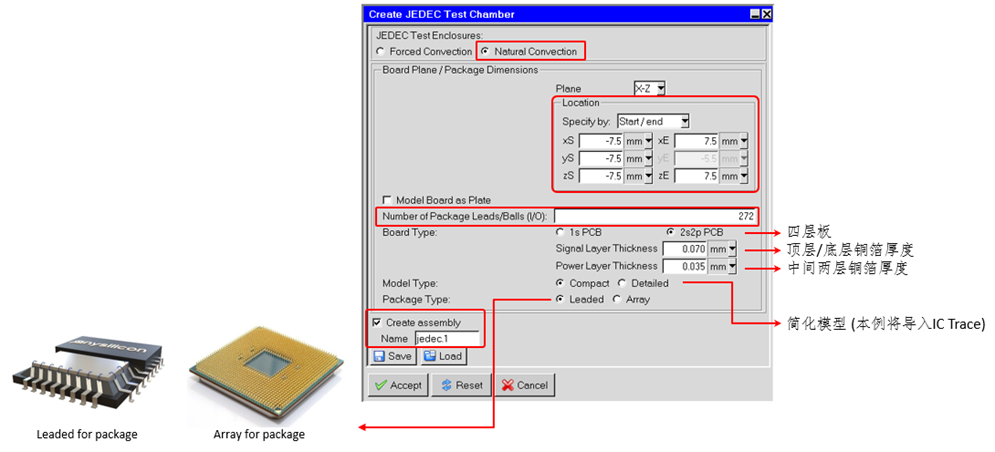

本章以芯片封装为案例,说明如何利用Ansys Icepak计算IC封装的Rja (芯片Die与空气间的热阻)、Rjb (芯片Die与电路板间的热阻)及Rjc (芯片Die与封装表面间的热阻)。

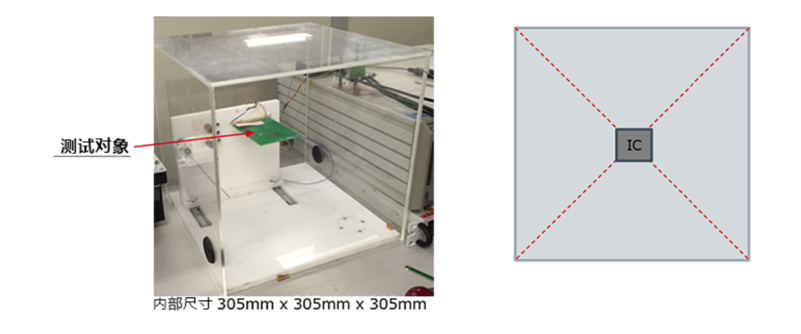

针对封装热阻而言,计算放置于JEDEC(美国联合电子设备工程协会)标准机箱内自然对流及强制队留下的热阻数据。部分内容参照了JEDEC测试系列的表准[JESD51]。Ansys Icepak为了仿JEDEC标准测试规范,所有设置皆按JESD51设置标准来设计与进行。

方案重点:

通过JEDEC标准仿真出芯片的Rja、Rjb及Rjc。

导入芯片封装ECAD → Compact + ECAD (非采用Icepak/JEDEC中Detail模型)

3

JEDEC是什么?

JEDEC(Joint Electron Device Engineering Council)是一个推动半导体元器件领域标准化的行业组织。半导体制造商以及电力电子领域的从业者不可避免地会涉及到很多行业标准。作为大原则,无论热相关的项目还是其他项目,其测试方法和条件等都要符合行业标准。其原因不言而喻:因为如果方法和条件各不不同,就无法比较和判断好坏。

在JEDEC标准中,与“热”相关的标准主要有两个:

JESD51系列:包括IC等的封装的“热”相关的大多数标准。

JESD15系列:对仿真用的热阻模型进行标准化。

JESD51-2A中规定了热阻测试环境。以下是符合JESD51-2A的热阻测试环境示例。

4

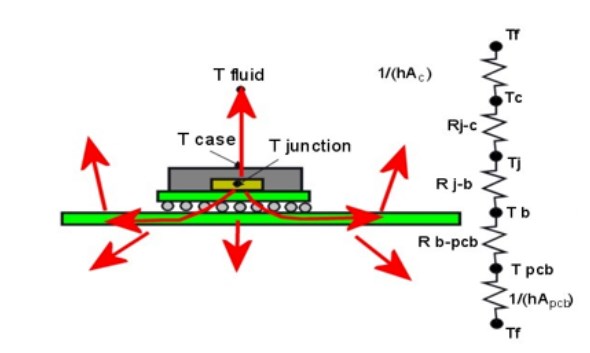

热阻概念

热阻值可用于评估电子封装的散热效能,是热传设计中一个相当重要的参数,有助芯片的散热设计。热阻值关系定义如下:

热阻值一般常用R或θ表示,其中Tj为接面位置的温度(JunctionTemperature);Tx为热传到某点位置的温度,例如环境温度(AmbientTemperature);P 为输入的发热功率。热阻大表示热不容易传递,因此组件所产生的温度就比较高。

由热阻可以判断及预测组件的发热状况。电子系统产品设计时,为了预测及分析组件的温度,需要使用热阻值的数据,因而组件设计者则除了需提供良好散热设计产品,更需提供可靠的热阻数据供系统设计之用。

5

JEDEC Board Size

(芯片大于等于或小于27mm)

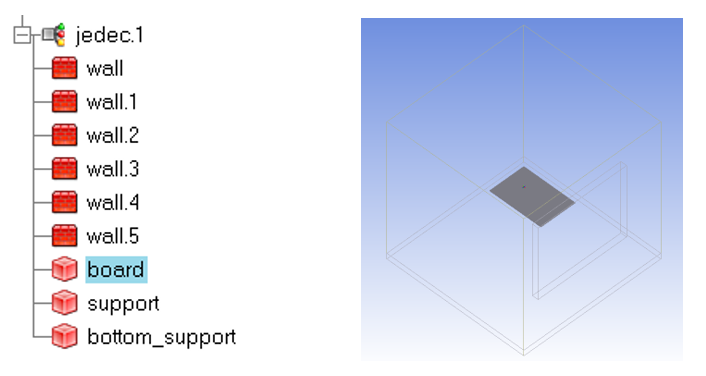

当Macro中的JEDEC设置完成后,Icepak会自动把测试模型建立出来,其中Board Size有两种可能。

当测试芯片尺寸小于27mm,Board Size=114.3mm*76.2mm

当测试芯片尺寸大于/等于27mm,Board Size=114.3mm*101.6mm

JEDEC IC ThermalResistance Test

6

芯片封装Rja的仿真计算

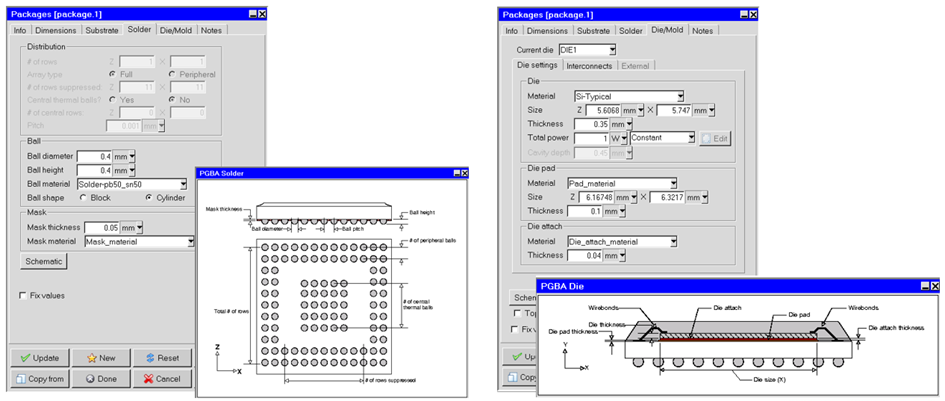

本案例IC封装尺寸取14.06mm×14.06mm×2.15mm(属于小于27mm的芯片),焊球个数 = 272颗/环境温度20C/ICDie发热功率=1.0W。

产生标准JEDEC测试腔体 (包含放置IC的Board),组件内的材料参数已默认标准属性,不需另外设置。

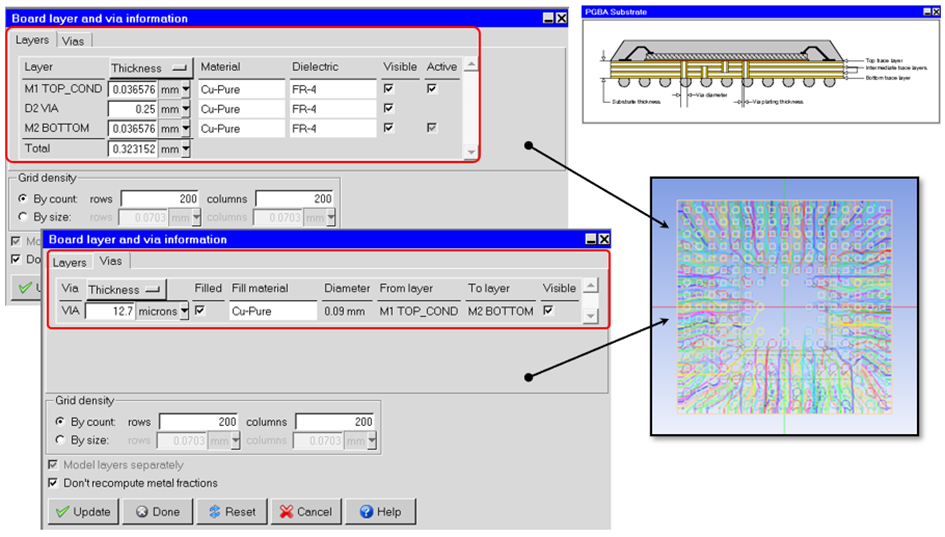

为了详细仿真芯片封装热组参数,建立的热模型建议导入ECAD设计的封装模型。

为了详细仿真芯片封装热组参数,建立的热模型建议导入ECAD设计的封装模型。

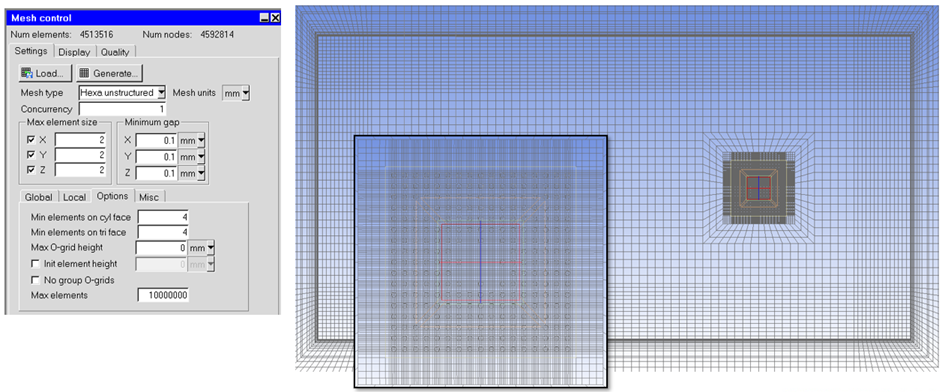

为了环境空间的准确性,网格数量设置达450万;环境20C。

7

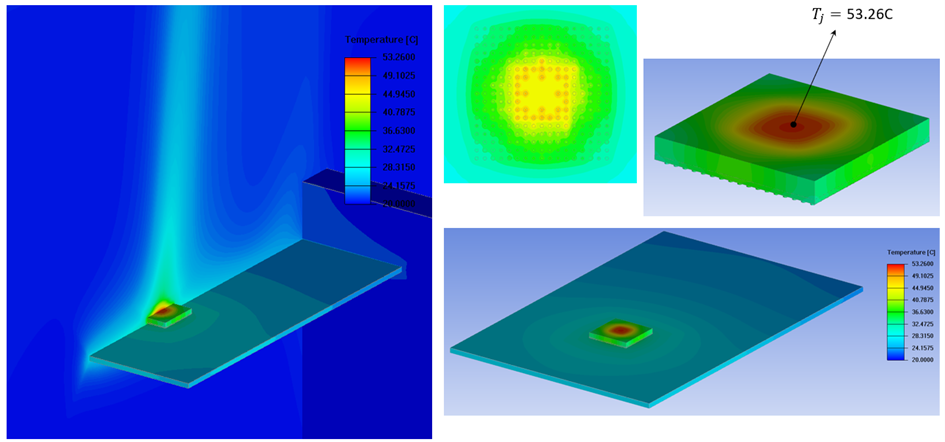

结果

根据上面结果,芯片封装Die的最高温度为53.26C,得到Rja如下:

| 风速, m/s | 0, 自然对流 | 1, 强制对流 | 2, 强制对流 | 3, 强制对流 |

| Tj | 53.26 | 49.86 | 48.12 | 47.14 |

| 热阻, oC/W | 33.26 | 29.86 | 28.12 | 27.14 |

Rjc及Rjb概念也如上有极为雷同之处,唯一特别要注意其于JEDEC中的模型规范。

(文章来源:莎益博CAE仿真)

![]()