半导体组件随着各种消费性通讯产品的需求提升而必须拥有更多功能,组件之间也需要系统整合。因应半导体制程技术发展瓶颈,系统单芯片(SoC)的开发效益开始降低,异质整合困难度也提高,成本和所需时间居高不下。此时,系统级封装(SiP)的市场机会开始随之而生。

采用系统级封装(SiP)的优势

USI 环旭电子一站式微小化解决方案

相较于SoC制程,采用系统级封装(SiP)的最大优势来自于可以根据功能和需求自由组合,为客户提供弹性化设计。以最常见的智能型手机为例,常见的的功能模块包括传感器、Wi-Fi、BT/BLE、RF FEM、电源管理芯片……等。而系统级封装即是将这些独立制造的芯片和组件共同整合成模块,再从单一功能模块整合成子系统,再将该系统安装到手机系统PCB上。

SiP整体制程囊括了着晶、打线、主/被动组件SMT及塑封技术,封装成型可依据客户设计制作不同形状模块,甚至是3D立体结构,藉此可将整体尺寸缩小,预留更大空间放置电池,提供更大电力储存,延长产品使用时间,但功能更多、速度更快,因此特别适用于射频相关应用如5G毫米波模块、穿戴式装置及汽车电子等领域。

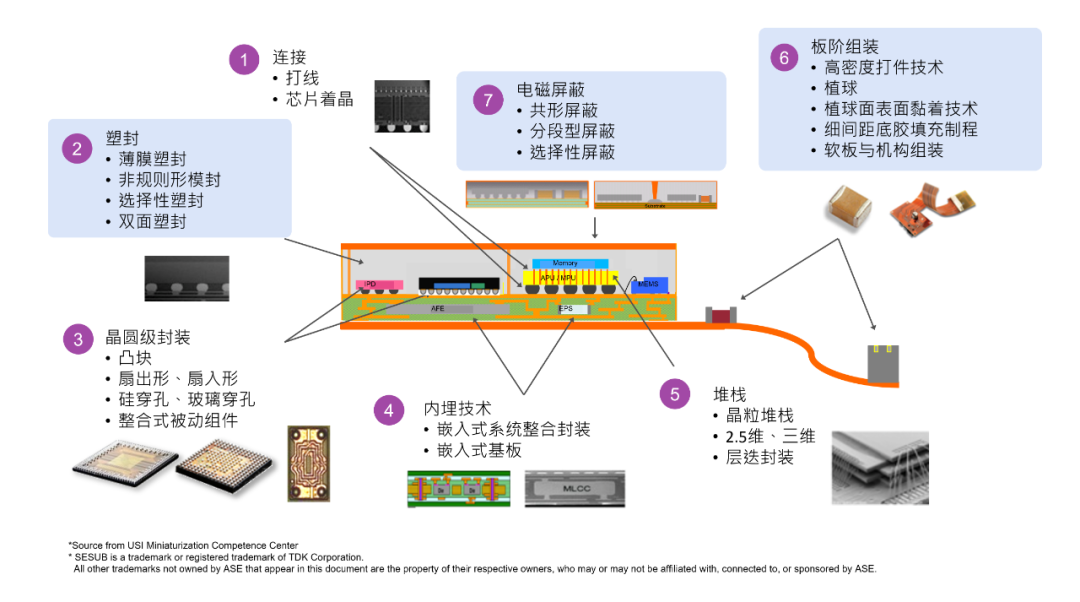

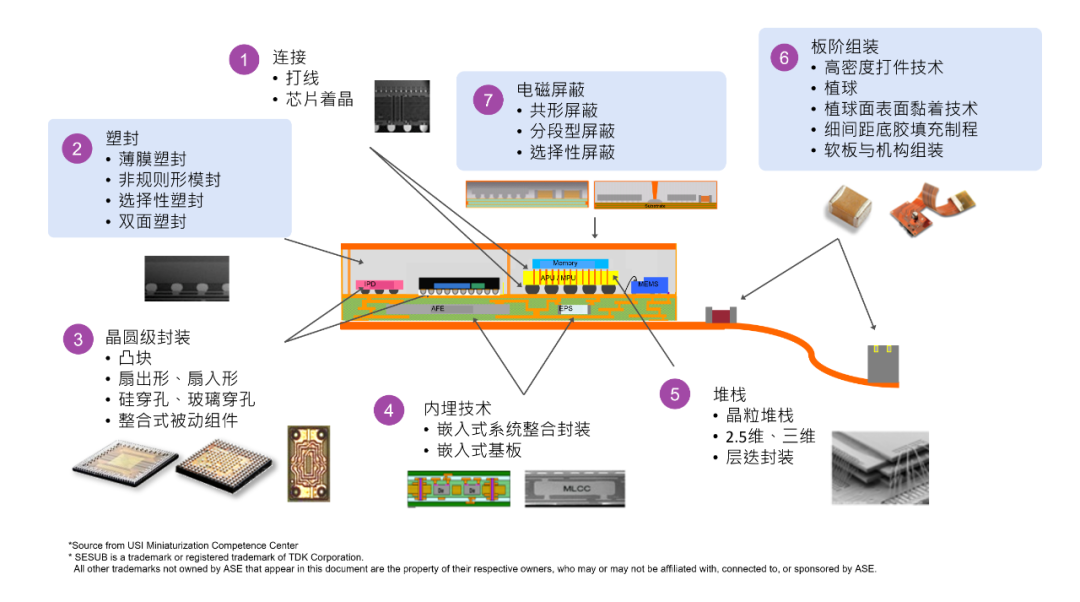

微小化制程三大关键技术

在设计中元器件的数量多寡及排布间距,即是影响模块尺寸的最主要关键。要能够实现微小化,最重要的莫过于三项制程技术:塑封、屏蔽及高密度打件技术。

系统级封装(SiP)制程关键技术

高密度打件

在高密度打件制程方面,环旭电子已达到约为婴儿发丝直径的40μm。以10×10被动组件数组做比较,大幅缩减超过70%的主板面积,其中的40%乃源自于打件技术的突破。

塑封 由于高密度打件采用微小化元器件与制程,因此元器件与载板之间的连结,吃锡量大幅减少,为提高打件可靠度,避免外界湿度、高温及压力等影响,塑封制程可将完整的元器件密封包覆在载板上。相较于一般委外封测(OSAT)塑封约100颗左右,环旭电子的系统级封装塑封技术,则是可容纳高达900颗组件。

「共形」及「分段型」屏蔽

另一方面,系统级封装模块需要高密度整合上百颗电子组件,同时避免与PCB主板上其他组件相互干扰。此外,在模块外部也必须解决相同的干扰问题。因此,必须透过一项重要制程来形成组件之间的屏障,业界称之为共形屏蔽(Conformal Shielding)和分段型屏蔽(Compartment Shielding)。 在业界普遍常见的金属屏蔽罩,每一段均需要保留约1mm宽度的焊盘与排除区域 (Keep-Out Zone),环旭电子的共形及分段型屏蔽仅需10%的宽度。以一个多频4G模块为例,可为其他组件腾出超过17%的空间,并可屏蔽40-50 dB的电磁干扰。

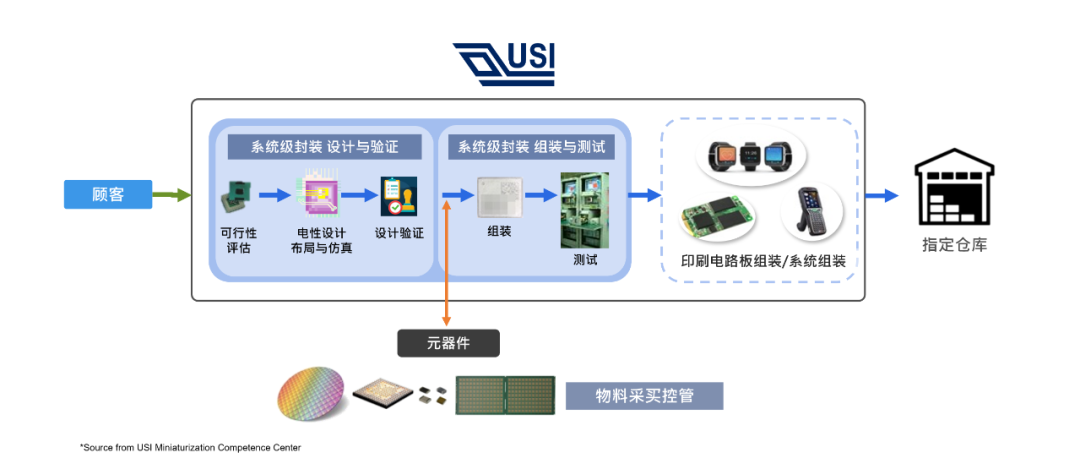

一站式系统级封装服务

凭借超过10年的系统级封装经验,环旭电子至今不仅仅在关键制程取得突破,我们已经能为客户提供「一站式系统级封装服务」。从电子/射频的SiP设计、板端及模块的仿真验证、封装制程、系统级测试,甚至包含物料管控与将成品送达指定仓储,完整满足客户的多样化需求。

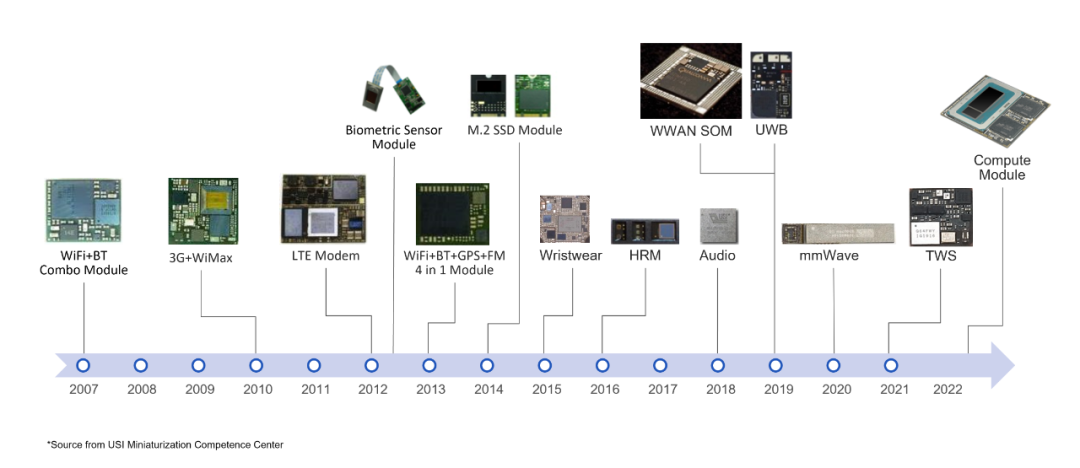

USI环旭电子微小化制造经验 – 应用产品

面对客户在系统级封装产品的设计需求,环旭电子具备完整的数据库,可在整体微小化的基础上,提供料件及设计的最佳解,接着开始进行电路布局(Layout) 与构装(Structure)设计。经过封装技术,将整体电路及子系统塑封在一个仅仅「芯片」大小的模块。 高密度与高整合的模块化设计前期的模拟与验证特别至关重要,环旭电子提供包含载板设计和翘曲仿真、电源/讯号完整性分析(PI/SI)、热流模拟分析(Thermal)等服务确保模块设计质量。实验室内同时也已经为系统整合验证建置完整设备,协助客户进行模块打件至主板后的射频校准测试与通讯协议验证,并提供系统级功能性与可靠度验证。

SiP模块可靠度及失效分析

由于内部线路和基板之间的复杂链接,当模块出现问题时,分析微米级组件的异常变得特别具有挑战性,尤其是在电性测试期间,其他部件的导电性会影响测定结果。而且某些异常污染可能仅仅只有几奈米的厚度,如:氧化或微侵蚀,使用一般的光学或电子显微镜根本无法发现。为了将制程问题降至最低,环旭电子在SiP模块失效分析领域持续强化分析能力,以X射线检测(3D X–ray)、材料表面元素分析(XPS) 及傅立叶红外线光谱仪(FTIR)等三大品管仪器找出解决之道:

失效分析三步骤 X射线检测(3D X–ray):透过失效分析当中的X–ray检测,我们可以深入确认模块是否有封装异常,并且找出异常组件的位置。 材料表面元素分析(XPS):接着,利用XPS针对微米等级的模块表面进行更细微的元素分析,以此探究模块出现电阻值偏高、电性异常、植球脱球及镀膜脱层等现象是否来自于制程的氧化或污染。 傅立叶红外线光谱仪(FTIR):如明确查找到污染物目标,则可再接续使用FTIR进行有机污染物的鉴定,定义出问题根源究竟是来自哪一个阶段,以此找出正确解决方案。

突破「微小化」竞争格局

凭借异质整合微小化优势,系统级封装能集成不同制程技术节点 (technology node),不同功能、不同供货商,甚至是不同半导体原材料的组件,整体可为产品节省约30-40%的空间,也能依据需求客制模块外型并一定程度简化系统主板设计,让主板、天线及机构的设计整合上更加有弹性。同时,相较于IC制程的开发限制,系统整合模块可以在系统等级功能就先进行验证与认证,加速终端产品开发,集中系统产品研发资源。 SiP技术是全球封测业者最看重的焦点,系统级封装(SiP)技术的突破正在影响产业供应链、改变竞争格局。环旭电子从Wi-Fi模块产品就开始进行布局、站稳脚步,积累多年在射频、穿戴式装置等产品的丰富制程经验,透过「一站式系统级封装服务」协助客户实现构想。

(文章来源:环旭电子)

![]()