4 月 19 日消息,SK 海力士宣布和台积电签署谅解备忘录(MOU),推进 HBM4 研发和下一代封装技术,目标在 2026 年投产 HBM4。

根据双方签署的谅解备忘录,两家公司初期目标是改善 HBM 封装内最底层基础裸片(Base Die)的性能。

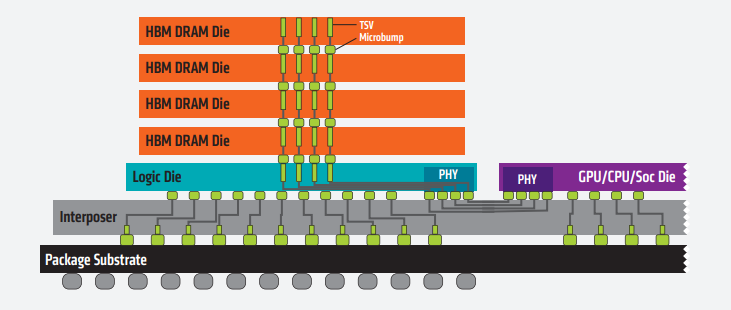

HBM 是将多个 DRAM 裸片(Core Die)堆叠在基础裸片上,并通过 TSV 技术进行垂直连接而成,基础裸片也连接至 GPU,在 HBM 中扮演非常重要的角色。

包括 HBM3E(第五代 HBM 产品)在内,SK 海力士旗下 HBM 产品的基础裸片此前均采用自家工艺制造,而从 HMB4(第六代 HBM 产品)开始,该公司将采用台积电的先进逻辑(Logic)工艺。

消息称双方将会展开紧密合作,尝试使用台积电的 CoWoS 技术封装 SK 海力士的 HBM 产品,从而在性能和功效等方面,进一步满足客户的定制化(Customized)HBM 产品需求。

SK 海力士今年 2 月还制定了 One Team 战略,通过台积电建立 AI 半导体同盟,进一步巩固在 HBM 领域的优势。

▲ HBM 内存结构示意图

此外,未来 AI 半导体将从 HBM 时代的 2.5D 封装走向 3D 堆叠逻辑芯片和存储芯片的新型高级封装。存储企业同芯片代工 + 高级封装企业的合作有利于相关研发推进。

![]()