从 2D 扩展到异构集成和 3D 封装对于提高半导体器件性能变得越来越重要。近年来,先进封装技术的复杂性和可变性都在增加,以支持更广泛的设备和应用。在本文中,我们研究了传统光刻方法在先进封装中的局限性,并评估了一种用于后端光刻的新型无掩模曝光。

后端光刻的新挑战

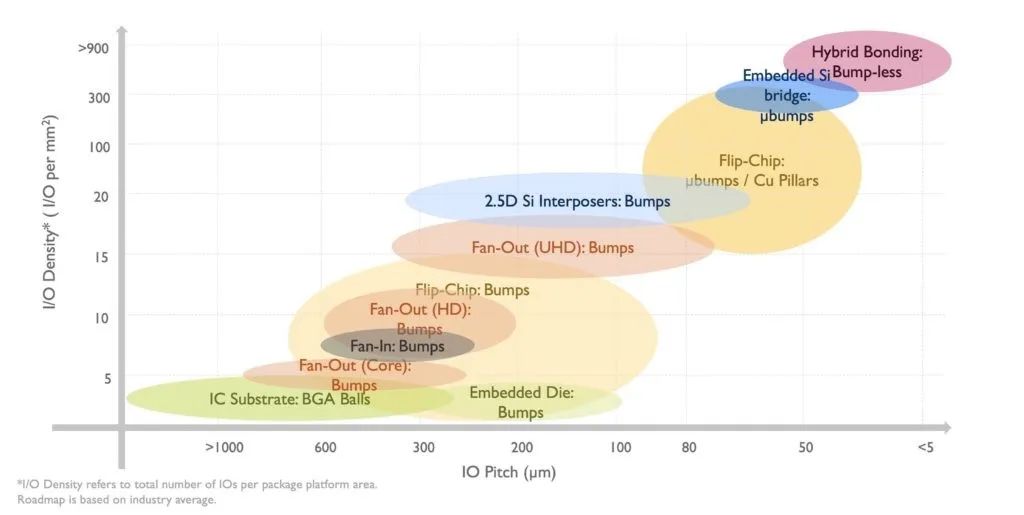

随着异构集成越来越多地用于半导体开发和创新,后端光刻技术的要求也在不断增长,如图 1 所示。封装内更多的再分布层 (RDL) 推动了对更细的RDL线/间距(L/S)以及更小的微凸点和微柱的关键尺寸的需求。这使得封装和基板级别的集成设计规则更加严格,这增加了叠加和芯片移动的风险,可能导致寄生效应和产量损失。

与此同时,为了提高封装性能,I/O 的数量也在不断增长,从而导致更大的硅片占用空间和光罩缝合。这推动了对 I/O 凸块和互连减小间距的需求。后端光刻也需要在垂直侧壁图案中提高覆盖精度和高焦深 (DoF)。还必须满足新的要求,包括尽量减少由于扇出晶圆级封装 (FoWLP) 中的晶圆变形而导致的图案失真和芯片移位,以及在保持高DoF和高分辨率的同时在厚和薄抗蚀剂上进行图案制作。

图 1:先进的封装架构正在推动 I/O 密度的大幅增加和 I/O 间距的减小,这对后端光刻提出了新的要求(来源:Yole Développement )。

尽管从较小的小芯片重新集成较大的裸片已显示出优于单片 SoC 技术的众多优势,包括更大的设计自由度,但这种方法将复杂性转移到了集成中,并随之转移到了光刻工艺中。小芯片设计和各种集成方案(硅上、嵌入或封装)的持续创新可能包括多个图案层次,这增加了集成的复杂性。在后端光刻中,设计灵活性和同时采用芯片和晶圆级设计的能力的重要性增加,也必须得到解决,以缩短开发周期,支持各种先进的封装平台。

传统图案化方法的回顾

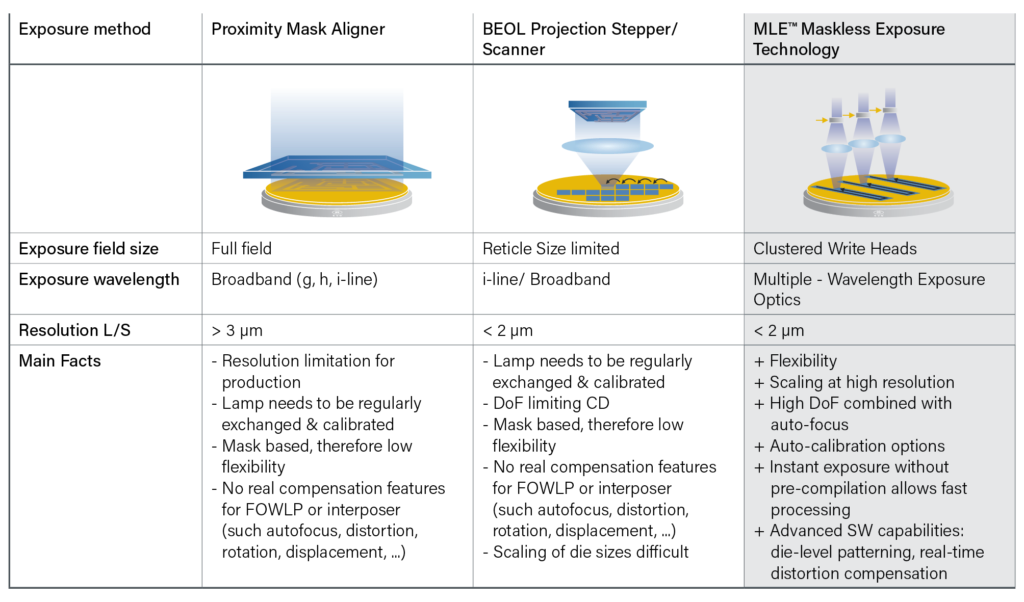

有几种曝光方法可用于高级封装应用(图 2)。其中包括掩模对准器,它通过掩模将图案直接曝光在基板上,掩模与光敏、涂有抗蚀剂的晶片非常接近。最小图案尺寸由掩模和晶圆之间的曝光间隙决定的。掩模和抗蚀剂表面的紧密接近将使图案更小;但是,间隙太近会导致掩模污染并导致良率问题。

图 2:用于高级封装应用的各种后端光刻方法。

图 2:用于高级封装应用的各种后端光刻方法。

另一种曝光方法是生产线后端 (BEOL) 步进器,它再看掩模/掩模版和晶圆之间使用投影光学器件寸,使其尺寸小于掩模对准器所能达到的尺寸。然而,由于它是一种基于掩模的曝光方法,步进机必须处理由模塑和其他因素引起的芯片放置和芯片移位变化的不准确性。此外,静态曝光系统的给定光罩尺寸和光学尺寸限制了曝光区域。这对于较大的芯片中介层制造来说尤其具有挑战性,其中缝合线或掩模版曝光场的不匹配重叠区域会影响 RDL 内的电气性能。

此外,与掩模相关的成本对整个图案化工艺来说是一个重要的额外成本因素。任何先进的产品设计组合,例如异构集成应用程序中的设计组合,都会增加多个掩模的层次。因此,掩模和掩模库存/清洁室存储在整个生产成本中占了很高的比例。汞灯的更换成本加起来会很高。新的物理掩模组的等待时间,以及高产品组合设计的新设计概念的整体证明,本质上会导致传统的基于掩模的生产环境的开发周期延长。

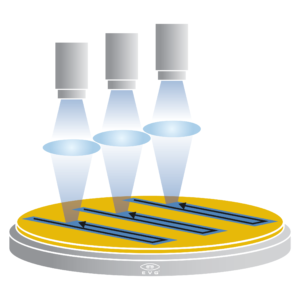

为了解决异构集成的光刻需求,我们开发了一种名为LITHOSCALE的新型无掩模曝光系统,该系统采用无掩模曝光 (MLE) 技术。LITHOSCALE结合了高分辨率(<2μm L/S),没有曝光场的限制,强大的数字处理,实现了实时数据传输和即时曝光,以及高度可扩展的设计,支持大批量的生产。该系统的高精度与无失真的高强度光学元件和亚纳米范围的载物台运动精度相匹配,从而确保在整个基板上进行无缝投影。LITHOSCALE 还采用动态对准模式和带自动对焦的芯片级补偿,以适应基板材料和表面变化。

图 3:LITHOSCALE 独特的集群曝光配置可以轻松添加曝光头,以适应不同的吞吐量需求和基板尺寸。

这种无掩模曝光技术以平行扫描方式曝光一个或多个宽条,并通过紧密集成的集群写入头配置适应任何晶片尺寸,直至面板,如图 3 所示。一个多波长的高功率紫外光源可以支持所有市面上的抗蚀剂。吞吐量与布局复杂性和分辨率无关,而且无论光刻胶极性如何,都能实现相同的图案化性能。最后,数字掩膜图案以亚微秒级的时间精度被投射到基片表面。像大多数现代镜头一样,LITHOSCALE成像系统是衍射限制的,它支持+/-12μm的景深(DoF)。

除了宽DoF之外,亚微米级精确自动对焦将可用的动态对焦范围扩大到 100μm 以上。通过卡盘定位和晶片夹持,能在更大范围的晶片位置上控制焦点位置的能力,从而能够补偿弯曲和翘曲的基板。

动态曝光方法和主动模位补偿

由于基于掩模的光刻方法无法控制小于曝光场的失真,因此它们面临非线性、高阶基材畸变和芯片移位相关问题的困难,尤其是在晶圆上进行芯片重组后,这是典型的扇出晶圆级封装(FOWLP)。使用 LITHOSCALE 上的动态对准模式进行光刻实验,以评估晶圆级失真补偿的性能以及无掩模曝光系统上的主动芯片图案化的性能。

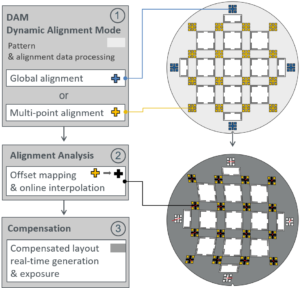

图 4:高级失真补偿流程示意图。

图4直观地显示了高级失真校正功能和动态对齐模式的工艺流程。动态对准包括全局和多点晶圆对准选项,通常可以随机放置多达 16 个对准标记(标记为蓝色和黄色)为了覆盖基板上最关键的区域并补偿全局失真。在未对准测量之后,位移矢量会进一步并行编译,然后再对设计进行实时插值和渲染。

因此,曝光的图案得到了全部的误差补偿,就不会产生重叠或未覆盖的区域——可能有最小程度的错位,这不影响图案化工艺的水平。在通过动态对齐模式补偿多点对齐的16 个标记(黄色)的实际位置后,显示了在极端非典型错位(用红色箭头指示)示例之后的补偿布局(深灰色)的可视化结果。

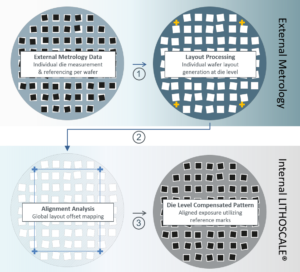

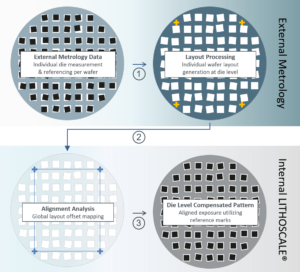

图 5:Die 级补偿流程示意图。

当考虑在晶圆上重构后引起的芯片失真误差时,高级失真功能也应在芯片层面上应用,其中主动补偿和重新布线结果严格依赖于外部计量数据。失真补偿算法包括旋转、缩放、剪切和平移(移位)的数学校正。对于模具放置误差补偿,该模型将模具内的变形限制在模具的刚体上,这通常由每个芯片的两个(外部)对齐点表示。由于转换过程的即时性,动态二进制图案生成在曝光前对每个基板单独从外部获取的每个芯片的计量数据进行补充,以补偿由处理或预处理引起的重叠/定位误差,排除了潜在的热影响。芯片级补偿的简化数据完整性流程如图 5 所示。

同时,LITHOSCALE 可以实现实时个性化晶圆级布局以及同时构建单个芯片布局;特别是功能性和直接可读的加密代码或主动图案化的熔断图,以优化器件分档,用于工艺或器件跟踪和记录,从而提高整体良率。

子网格中的图案化模块化和重要定位

LITHOSCALE的分辨率针对典型的后端分辨率,可精细控制照射线及其间隙 (L/S <2μm),同时保持 CD 均匀性 (CDU <10% CD) 和任意结构的位置准确性。这种精度与系统的无失真光学元件和载物台放置精度相匹配,可确保在整个基板上进行无缝投影。曝光可以在强度控制和精确的光源光谱调谐方面以非常高的自由度进行,以实现最佳的吸收和可靠的处理,适用于广泛的商业化的以及新型的光刻胶。

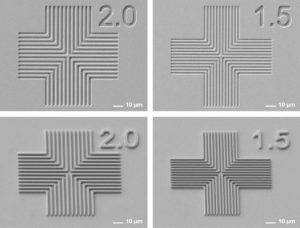

图 6:SEM 结果拼贴:在 1μm 厚的正AZ MIR 701 上进行线空间分辨率测试(上),在 2μm 厚的负 AZ nLOF 上进行线空间分辨率测试(下)。

曝光光源在 375nm 和 405nm 的波长光谱下工作,允许混合和匹配波长以模仿已知良好的工艺配方或根据特定客户需求定制曝光。两种波长可以同时以任意混合物形式应用,因此可以实现薄抗蚀剂图案化(包括正性、负性、聚酰亚胺、可图案化电介质、干膜甚至 PCB 材料),并且还支持在晶圆中通常遇到的高纵横比的厚光刻胶曝光级封装、3D MEMS 图案化、微流体和集成光子学应用。图6显示了一系列SEM图像,上面是1μm厚的AZ MIR 701正极抗蚀剂上的标准线空间分辨率目标,而下面的结果显示了2μm厚的负极抗蚀剂AZ nLOF上的线空间分辨率测试。在这两种情况下,1.5μm的L/S结果是通过进一步的工艺优化实现的,涉及到减少表面反射效应,这可以通过应用抗反射涂层或修改基片材料特性来实现。

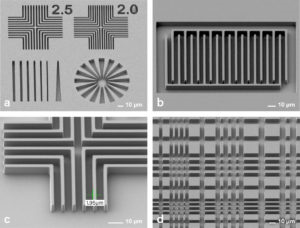

图 7:(A) 8μm 厚 TOK P-W1000T 的基线评估,(B) 具有 5μm L/S 的曲流,(C) 1:2 间距变化,(D) 水平和垂直方向的 L/S 变化与比率1:1、1:2、1:3、1:4。

DoF也可以被精细控制,以实现陡峭的侧壁,从而保持所需的抗蚀剂的3D轮廓,或防止边缘顶和脚。大的工作距离和自动适应性聚焦确保了整个曝光面图案的均匀性。常用的TOK P-W1000T抗蚀剂用于细线和芯线RDL的制作,以展示各种线和间距的图案性能以及侧壁图案的质量。图7显示了基线评估的SEM图像的例子,展示了:(A)针对8μm薄膜厚度的2μm L/S分辨率,(B)带有蜿蜒图案的5μm L/S分辨率,(C)1:2比例的间距变化,以及(D)水平和垂直方向的1:1、1:2、1:3和1:4比例的L/S变化。

概括

3D 和异构集成的采用导致封装复杂性和可用封装选项的数量增加。基于掩模的光刻解决方案不再适用于许多先进的封装应用,因为它们无法在分辨率和成本之间做出必要的权衡,受到曝光场大小的限制,并且/或者面临基板变形和芯片移位相关问题的困难。采用 MLE 技术的 LITHOSCALE 通过将高分辨率与无曝光场限制、可实现实时数据传输和立即曝光的强大数字处理以及高度可扩展的设计相结合,解决了先进封装的光刻需求,而无需基于掩模的高成本曝光方法。

![]()