芯片正在变得越来越复杂。开发者们一方面要应对摩尔定律趋近极限所带来的挑战,一方面要努力改进功耗、性能、面积(PPA),以及低延时目标。芯片开发者们始终坚持不断创新,从而应对SysMoore时代所面临的挑战。

MulTI-die芯片系统被细分成多个功能电路模块,这些电路块被称为小裸片(small die)或者小芯片(chiplet)。这些小芯片通常采用不同的工艺节点制造,并被集成到单个封装中。它能够满足严苛的PPA目标,是值得开发者努力的方向。先进的芯片封装技术在创新过程中必将起到主要作用。

MulTI-die系统级封装(SiP)具有以下优势:

可开发具有更多功能的产品

可通过更换裸片快速开发出多个SKU

可使用经过验证的裸片,减少开发风险

与使用两个独立的芯片相比,mulTI-die吞吐量更高,系统功耗更低

可优化系统外形尺寸,降低系统成本

与使用两个独立的芯片相比,裸片间的低延迟可以提高系统性能

封装行业有一系列技术可支持mulTI-die设计,例如:标准的2D封装、2.5D先进封装,以及3D堆叠裸片,但没有哪个封装技术是可以适合所有产品的。选择哪种封装方式将取决于产品的PPA和成本目标。

本文将简单介绍几种最新的多芯片模块(MCM)封装类型,并重点阐述die-to-die(D2D)IP如何通过这些封装来更好地支持设计流程。

四大先进芯片封装类型

下一波系统设计浪潮将以先进封装中的小芯片为主导。这些小芯片本质上也是集成电路,专门用来与其他裸片一起打造更大、更复杂的芯片,且可以被集成到先进的MCM封装中。小芯片通常由可重复使用的IP块组成。

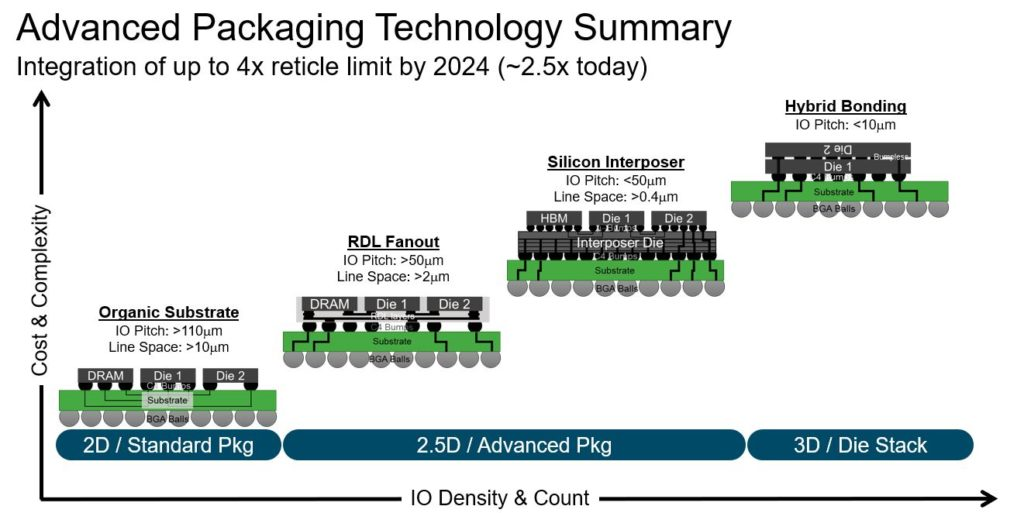

不同的封装类型在组装、密度和复杂性方面各不相同。图1介绍了主要的封装类型以及它们在不同应用中的优势和劣势。

▲ 图1:主要的先进封装类型概览

有机衬底

有机衬底可以支持低密度的IO排布,D2D连接较少。这种2D类型的标准封装相对便宜,在半导体行业中使用广泛。与2.5D和3D封装不同,有机衬底封装并不存在脆弱的微凸块,并且由于工艺已十分成熟,所以往往良率更高。它具有可测试性功能(对已知合格裸片进行低成本晶圆级筛选),但无法对故障连接进行测试和修复。

此外,有机衬底还具有良好的散热性和低翘曲性,支持大规模SiP集成,且无掩模板限制。

重分布层(RDL)扇出

相对较新的RDL扇出型(Fan-Out)封装尚未得到广泛使用,其密度与硅中介层相似,但复杂性和成本却更低。扇出是一种先进封装类型,可以组装一个或多个裸片,从而为各种物联网、网络和计算应用带来更好的性能和更多的IO。RDL由铜金属连接线组成,将封装的一部分与另一部分进行电气连接。在RDL扇出型封装中,RDL可向内和向外布线,这使得封装更薄且能拥有更多的IO。

硅中介层

在硅中介层中,连接裸片的地方叫做中介层,用来连接两个裸片。这种2.5D型封装通过使用微凸块(一种堆叠裸片垂直互连技术)实现密集连接。由于这种封装类型的组装十分复杂,加上微凸块脆弱易损,因此存在较多的良率问题。封装厂商通过质保措施和D2D接口测试及修复机制解决了这个问题。硅中介层拥有数千条并行的线路,这些线路可用于测试连接性、确定是否存在中断,并且能够在需要时重新布线。例如,如果一个接口有1000条线路,那么在设计PHY时就要当作有1100条线路,提供10%的冗余,以便在发生故障时可以重新布线。但硅中介层很难为已知合格裸片筛选晶圆。此外,这种封装类型减少了热耗散,并且中介层的大小受限于掩模板的尺寸。

混合键合封装

作为一种3D堆叠封装技术,混合键合封装实现了最高的密度和电源效率。它提供用于连接的硅通孔(TSV),将两个晶圆粘合到一起并作为一个整体发挥作用,如此一来,驱动通道时就不会浪费功耗,并且可以根据需要降低每个IO的功耗。与中介层相比,混合键合技术对复杂性和成本提出了更高的要求。这种技术非常适用于需要大量计算能力和低延迟的AI训练引擎等应用。在混合键合封装中的处理器上堆叠内存,可以提供所需的性能并满足低延迟要求。

D2D连接:推动力

虽然先进封装方案让开发者能够按照SysMoore时代的需求扩展和发展他们的产品,但D2D连接也起到了推动作用。过去,开发者会先创建SoC,然后再操心封装问题。如今,他们必须采用协同开发的方法将系统、裸片和封装结合到一起,并确保它们都能按照预期协同工作。是什么将所有这些部分都连接到一起了呢?

答案是D2D接口。

D2D接口是一个很小的模块,支持封装两个或两个以上裸片之间的通信。这种接口需要针对每个特定封装类型的特点进行优化。例如,中介层不支持通道之间极高的速度,高速D2D接口IP则可以填补这一空白。同样地,有机衬底的通道特性更好,可支持更长的传输距离和更高的数据速率,因此可以选择接口IP。

D2D接口行业相对年轻,许多接口是以专有的方式进行开发,只锁定一个产品。使用标准可以确保您能够不断改进自己的产品,且无需担心互操作性问题或其他开发风险。

四个不同的联盟管理着整个封装生态系统的五个标准:

OIF管理的XSR标准,数据速率为112G/224G,适用于光学网络的2D封装。

CHIPS ALLIANCE管理的AIB标准,覆盖6G数据速率,适用于通常针对军事航空生态系统的桥接封装。

UCIe数据速率为16G/32G,适用于2D、2.5D和桥接封装类型。UCIe面向通过PCIe和CXL进行流式传输和聚合的扩展和拆分用例。

开放计算项目负责BOW和OHBI标准,二者的数据速率为8G/16G,适用于2D和2.5D封装。BOW面向关注成本的聚合用例,而OHBI则面向数据中心高密度规模和拆分用例。

随着时间的推移,其中有些标准可能会因市场需求而变得不再那么重要。在所有这些标准中,UCIe有可能成为一个真正通用和全面的D2D接口标准。除了提供最引人注目的PPA指标,这项标准还涵盖了最广泛的用例和所有的multi-die芯片封装类型。UCIe是一个完整的协议栈,支持原始用户定义的流式传输、PCIe(非相干)和CXL(相干)。此外,UCIe还具有前瞻性,支持每个引脚高达32Gbps的数据速率。这项新兴规范赢得了横跨所有行业领域的广泛生态系统的支持,其中包括超大规模厂商、CPU供应商、代工厂、外包半导体组装和测试(OSAT)、IP供应商和聚合商。

多种基于标准的D2D接口组合

新思科技提供业界最广泛的D2D标准接口IP,为各类标准组织做出了贡献,并助力企业发挥不同封装类型的优势。新思科技D2D IP解决方案包括:

完整的112G XSR IP解决方案,包括多通道PHY和一个具有前向纠错和重放功能的D2D控制器,可提供可靠的网络运行中心(NOC)到NOC链接

完整的UCIe IP解决方案,包括带宽高达4Tbps的多模块PHY,可支持标准封装和先进封装

支持流式传输、CXL和PCIe协议的控制器,以及到CXS和AXI的桥接,实现NOC到NOC的无缝链接

Multi-die设计能够满足HPC和AI等计算密集型应用的可扩展解决方案的需求,即在不影响成本或良率的情况下提高性能。在SysMoore时代,系统和规模的日趋复杂推动着持续创新,先进芯片封装技术作为代表之一至关重要。

![]()