我们产品在做验证时,经常会遭遇到电磁干扰(EMI)的问题,有时处理起来需花费非常多的时间,许多工程师在对策电磁干扰时也是经验重于理论,知道哪个频段要对策那些组件,但对于理论上的分析却很欠缺。

开关电源的电磁干扰测试可分为传导测试与辐射测试,一般开关电源的传导测试频段是指150K~30MHz之间,而辐射干扰的频段是指30M~300MHz,300MHz之后的频段一般皆不是电源所产生,因此大都可以给予忽略。

下面内容章节包括开关电源的传导测试法规,测试与量测方式,基本概念,抑制传导干扰的滤波器设计,布线与变压器设计等章节。

02 传导测试的法规

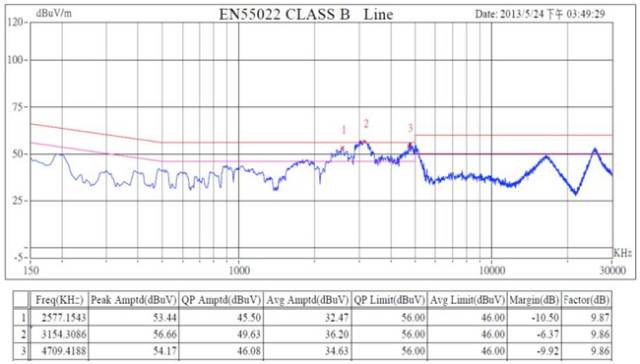

传导的法规因产品别的不同,其所适用之条文亦不同,一般是使用欧洲的EN-55022或是美国的FCC part15来定义其限制线,又可以区分为CLASS A与CLASS B两种标准,CLASS A为产品在商业与工业区域使用,CLASS B为产品在住宅及家庭区域使用,笔者所设计的产品为3C的家用电源,传导测试频段为150K~30MHz,在产品测试前请先确认申请的安规为何,不同的安规与等级会有不同的标准线。

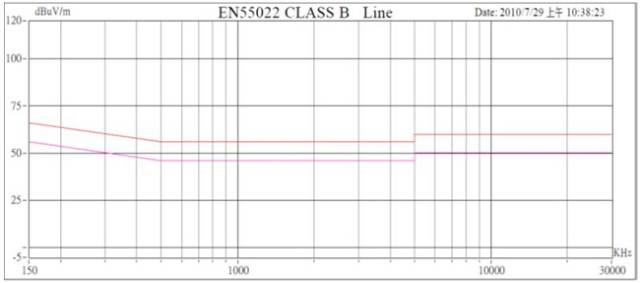

图1举例为EN-55022 CLASS B的限制线图,红色线为准峰值(QP, Quasi-peak)的限制线,粉红色为平均值(AV, Average)的限制线,传导测试最终的目的,就是测试的机台可以完全的低于其限制线,不论是QP值或AV值;

一般在申请安规时,虽然只有在限制线下方即可申请,但多数都会做到低于2dB的误差以预防测试场地不同所导致的差异,而客户端有时会要求必须低于4~6dB来预防产品大量生产后所产生的误差。

图1

图2

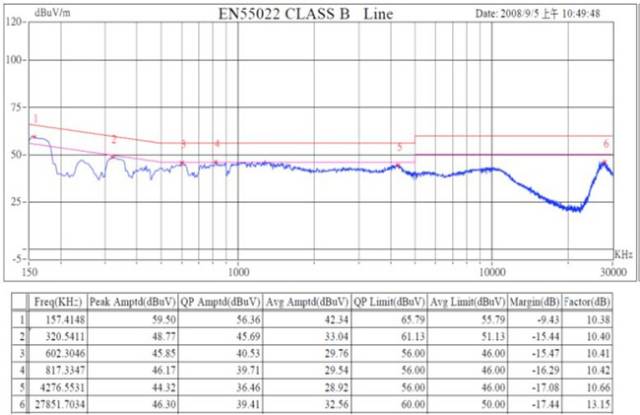

图2为一量测后的例子,一般量测时都会先用峰值量测,因峰值量测是最简单且快速的方法,量测仪器以9KHz为一单位,在150K~30MHz之间用保持最大值(maximum hold)的方式来得到传导的峰值读值,用此来确认电源的最大峰值然后再依此去抓最高峰值的实际QP,AV值来减少扫描时间,图2的蓝色曲线为准峰值的峰值量测结果,一般在峰值量测完后会再对较高的6个频率点做准峰值(QP)与平均值(AV)的量测,就如同图2所标示。

峰值与准峰值的差别在于:峰值量测是不论时常出现或是偶尔出现的信号皆被以最大值的方式置在接收器的读值中,而准峰值量测是指在一时间内取数次此频段的脉冲信号,若某频率的信号在一段时间内重复出现率较高,才会得到较高之量测值;平均值则是对此频段的振幅取平均值,典型的频谱分析仪可将带宽设定在30Hz左右来得到最真实的平均信号。

QP与AV相较于峰值,其侦测值必然较低,若一开始的峰值量测已有足够的余度则不用再做单点的QP和AV量测。

现在的IC为了EMI传导的防制,在操作频率上都会做抖频的功能,像是IC主频为65KHz,但在操作时会以65KHz正负6K做变化,藉此来将差模倍频的信号打散,不会集中在单一根频率上,如果没有抖频功能,差模干扰在主频的倍频时会呈现单根很扎实的QP与AV,如同图2的157KHz,仪器看到的峰值满高的,但读起来还仍有9dB以上的余度。

03 传导的测试与量测方式

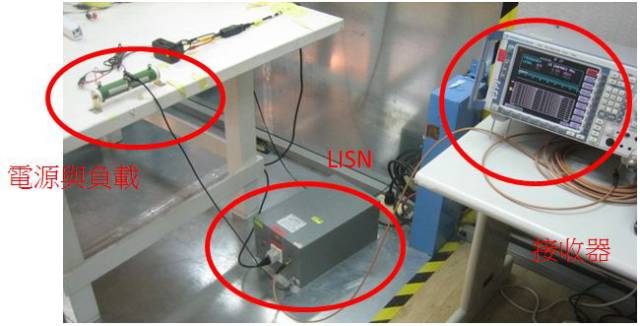

图3为测试传导的参考图示,此为通嘉内部的传导设备图示,待测物接仿真负载后放于桌面上,经由一输入线材(AC cable)连接LISN(线性阻抗稳定网络)与待测物,再将LISN的信号接至接收器,输入线材不得与地面接触,而待测物的负载需与待测物距离10公分,若周边需接电源时,其电源需接独立电源,不得与待测物使用相同电源,若电源为2PIN输入,则输出负载需接地以仿真系统下地。

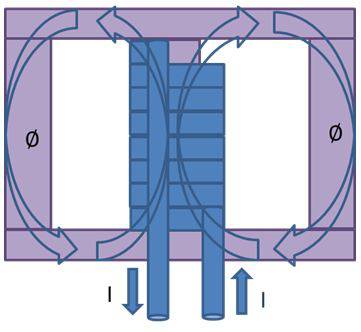

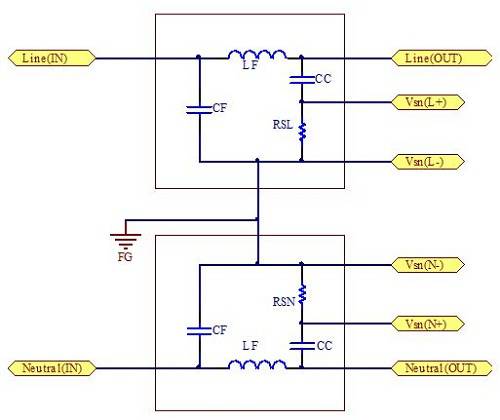

LISN(线性阻抗稳定网络)内部线路如图4所示,输入电源来源由左边进入LISN后,经由LF与CF来滤除电源的低频噪声,并由耦合电容CC与侦测电阻RSL/RSN来取得高频信号Vsn,再将此信号经接受器或频谱分析仪来得到其振幅的大小(dBuV)。

图3

图4

请记得输入线材不得与地面接触,笔者曾有过输入线材与地面接触与否,读值差了10dB左右的经验;另外,周边仪器的电源需使用干净且与主电源隔离的电源,否则很容易因共地而产生共模干扰,许多测试场地会直接拿一个延长线去使用外接电源给予周边,但此种方式仍有可能因共地而被干扰,若能使其接至另一个LISN是个较好的方式,因LISN内有LF与CF可作信号隔离。

04 对策EMI传导的基本概念

4.1 差模(DifferenTIal mode)信号与共模(Common mode)信号

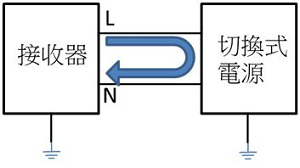

传导量测接法如图5、图6所示,是由接收器量测L/N/GND之间的频率与振幅大小而成,而信号存在于L与N之间的叫差模信号,如图5所示;而信号存在于L与FG或N与FG之间的叫共模信号,如图6所示,也可以说与FG形成回路的就叫共模信号。

一般电源的输入来源皆是取自L与N,因此在电源的电磁干扰设计中,差模成份的抑制极为重要,尤其是前频段150K~1MHz大多是由开关电源的主频与倍频出来的差模干扰。

图5

图6

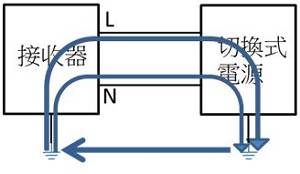

图7为一未对策前的传导测试结果,前端为IC的操作频率所引起的倍频差模干扰加上本体的共模干扰所形成,由图形可看出每根峰值之间的频率为100KHz,可判断此IC的操作频率为100KHz,而测量的读值是呈现由IC 100KHz的倍频做线性衰减,因此每100KHz就有一根因IC操作频率所造成的差模干扰信号,也可以说在前频段时,共模信号呈线性平面下降,而差模信号则迭加在共模的上方。

图7

图8为相同的机台在对策后测试结果,在对策后最差都还有6dB以上的余度,已可符合多数的客户要求。

一般在测试时,必须测试L与N两项,一般L与N的读值不会差异太大,若差异很大一般都是某项的共模能量较强所致。

测试的输入电压则是看申请的安规来决定,一般是用110V与230V来做高低压量测;另外,产品在确认传导测试时皆需要做长时间的烧机,有时会因烧机后磁性组件过热导致感量异常而让EMI变差。

图8

4.2 电磁干扰,电场干扰与磁场干扰

电磁干扰(EMI, Electrical MagneTIc Interference)可分为电场干扰与磁场干扰两种,电场与磁场是两种不同的性质,但两者之间的能量是会互相影响的,随时间变化的电场会产生磁场,而随时间变化的磁场也会产生电场,这些不断同相振荡的电场和磁场共同的形成了电磁干扰(电磁波)。

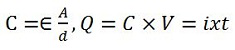

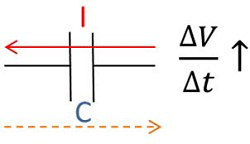

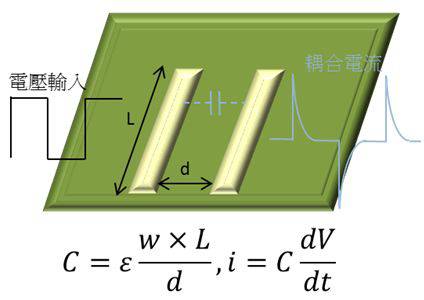

一般对于电场,我们可以用下面的电荷公式与电容公式来作解释,

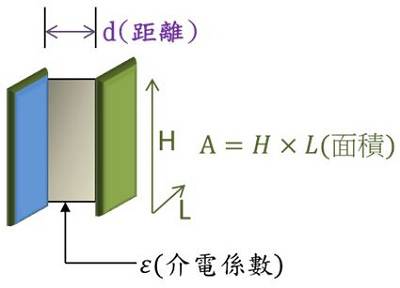

简单来说,任何的导体在电场下都可等效成一个带电的电容,其容值随着与周边另一个导体之间的距离/表面积/介质不同而有差异;如图9为两导体之间的电容图示,绿色导体与蓝色导体所等效的电容如图10所示,根据电容公式,容值会因两导体之间的距离愈远而变小,也会因两导体之间的截面积愈大而增大,而两导体之间的介质(介电系数)也会影响容值的大小。

图9 图10

图10

当电容二端的电位在时间之内存在一电压差时,则会根据电荷公式(电压/时间的变化,如图12)而产生一电流,如图11红色箭头所示,而任何产生的电流必需经由另一路径回到自己出发时的位置而形成一电流回路,如棕色虚线箭头所示,此因电压变动造成的电流回路就会引起电场干扰。

图11

图12

因此,改善电场干扰的方式,就是减少其回路电流的方法,根据上面两个公式,我们可以藉由将耦合电容减小,像是减少两个导体之间接触的面积/增加其距离/变更中间的介质等方式来减少电容效应,或是减小电压差或时间变化率来减少电场感应。

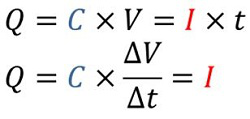

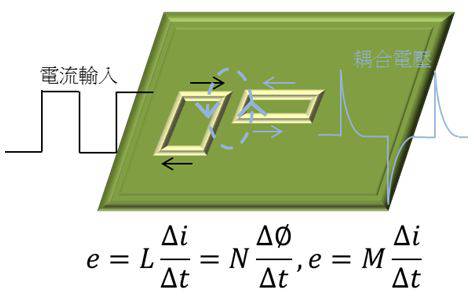

而对于磁场,我们可用安培右手/法拉第定律

来解释,当导体有电流流过时,在其周围就会依安培右手定律产生磁力线,如图13所示,因电流不可能单独存在,电流一定存在于回路之中,凡是电流流过的路径都会产生磁力线,而在一般的PCB板设计中(如图14所示),当电容形成一个电流回路时就会产生如虚线的磁力线,而磁力线经过的导体会因此产生感应电势,此即为磁场干扰。

图13

图14

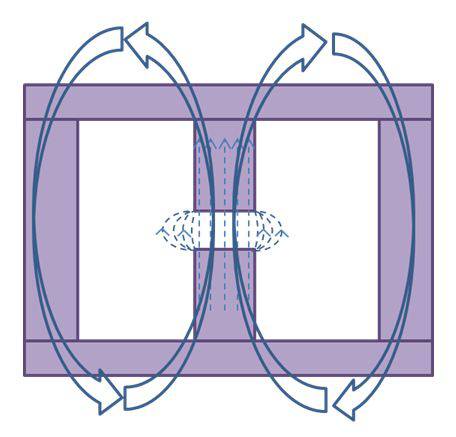

尤其是电流流经的导体在没有闭合回路的铁心时,因磁力线无法经由高导磁材料做回路,磁力线会经由外部空气做回路而让周围产生磁场(漏磁通),图15所示为一般变压器的磁力线,大多数的磁力线皆会经由高导磁材料(铁心)。

但在中间有气隙的地方就会有许多漏磁通产生(如图16虚线所示),而也有少部分漏磁通会经过与变压器垂直的地方,因此若有组件在变压器的正上方或下方,是很容易被此漏磁通干扰的。

图15

图16

因此,改善磁场干扰的方式,包括两部份,一是减少磁力线的能量,包括改变电流振幅/时间变化率等,另一是减少磁力线的影响,包括缩小电流回路,拉开两者之间的距离,导体面积等方法。

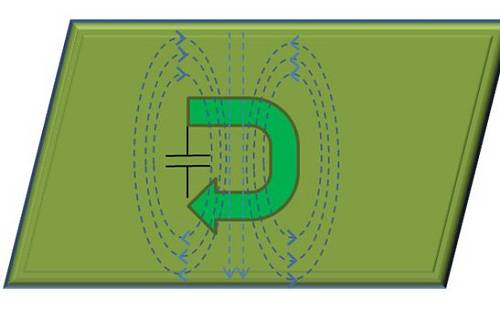

电场耦合效应如图17所示,在PCB板上有两导体时会有一等效电容效应,而当左端的布线有一时变电压产生时,其右边的导体会因电场耦合效应而产生一耦合电流,此耦合电流即是因电场效应所产生的电场干扰。

磁场耦合效应如图18所示,在PCB板上有两导体回路时,当左边的回路有一时变电流产生,其右边的回路也会因磁场耦合效应而产生一耦合电压(感应电势),此电压即是因磁场效应所产生的磁场干扰。

图17

图18

产生电场干扰的原因,在于带电体的电荷重新分布,因电荷改变后会让电容两端的电压改变而不断的充放电。产生磁场干扰的原因,在于流过导体的电流在不断改变,即电流产生的磁力线会使周围导体感应出电动势,造成磁场干扰。

电场与磁场的干扰起源于快速的能量(电压/电流)变化;而快速的能量变化可分两部份,一是能量本体的频率(变化率),一是能量本体的振幅(大小),而对策电磁干扰的方式不外两种,一是对策能量本体,像是抑制此能量的振幅或是改变其变化率,像是缓冲器,导通(截止)速度,更换组件的速度,变压器设计等。 另一是截断干扰的耦合路径,将干扰源封闭在电源本体里面,像是用LC滤波器,铜箔,外壳等,不论使用何种方式,目的都是为了达到电磁干扰可以通过法规的需求。

4.3 寄生组件的影响

在实际的电源产品中,到处都充满了寄生组件,包括组件本体的寄生组件与布线组成的寄生成分。当频率到MHz时,nH的电感与pF的电容会对EMI产生非常大的影响。

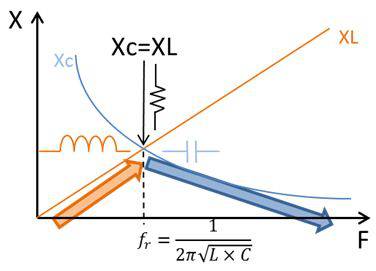

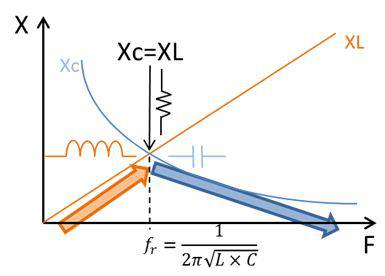

以一个环形电感来举例,多数的工程师只在意它的Al值,即绕了几圈后可以得到多少的感量,却没有去考虑到他的等效电容(ESC)与等效电阻(ESR),而在电磁干扰的领域,此等效电容与等效电阻却非常重要;理想的磁性组件,其阻抗应与频率成正比(Xl=2*pi*f*L),即频率愈高时其阻抗愈高,但在实际应用里,组件的等效电容却会抑制其阻抗特性。

如图19为一电感的阻抗与频率曲线,在频率低于共振点时,其阻抗会因频率上升而增加,但在过了共振点(Fr)后,阻抗却会因频率上升而变小,而无法达到预期的抑制效果。

图19 笔者在对策电磁干扰时将频段分为二部份, 10M以下的频段与10M以上的频段,在10M以下的频段, 其对策与变压器/滤波器/布线/结构等较相关, 而在10M以上的频段, 其对策与变压器/布线/滤波器/缓冲器(Snubber&Bead)/开关组件与速度/屏敝等较相关, 因布线/滤波器/变压器在高低频皆会影响,因此笔者在此先针对布线/滤波器/变压器等(10M以下)先做介绍。

05 布线(Layout)设计概念

由之前的介绍可知,电场干扰与磁场干扰是电磁干扰里最大的干扰源,不但布线的走线会大大的影响电场与磁场的耦合路径,也会因布线的寄生组件而影响电源的特性,因此良好的布线方式是从事电源设计不可缺少的能力之一,不但多数的电性问题皆因不良的布线导致,电磁干扰的好坏也与布线习习相关,不论是传导或辐射。

多数的布线工程师并不知道怎样的走线方式较好,而只认为每个节点都接到即可,愈资深的工程师则愈会对布线有所要求,以作者的经验,60%以上的电性不良皆是因布线所致,而在此将布线的基本概念概述如下:

5.1 安规距离与制程要求

此为最基本要求,任何产品皆需要达到安规规范,而不同的产线也会有不同的制程要求,像是组件本体大小,各组件之间的距离,接点大小,白漆…等,一般此规范会由各家布线工程师管控,因此在这里不做多述。

5.2 电源路径与信号路径需分开

在开关电源设计里,信号可分为大电流与小电流的,以 反激式(flyback)架构为例,大电流是由输入电源进来至滤波器,桥式,大电容,变压器,初级侧开关,次级侧二极管,输出电容到输出线材等走大电流的路径称为电源路径(power trace);而走小电流的路径就称为信号路径(signal trace),像是IC周边的组件或回授电路。

电压愈大会有较大电场的产生,而电流愈大则会有愈大磁场的产生,而周边组件,特别是良导体愈靠近此电场或磁场就会耦合愈大的能量,因此在做布线安排时,尽量让电源路径与信号路径分开来走,以免信号路径被干扰产生误动作,也避免干扰源藉由其他导体放大其干扰信号,在此将电源路径与信号路径分别说明如下:

5.2.1 电源路径的基本概念

把布线的路径想象成一条水流(即电流),水流自然会往河流愈宽的地方流(走线愈粗的地方),而且也自然会往低处流(往目标,即输出端流),在电源路径上的组件皆应该照顺序流过,否则会大大地衰减其作用。

电容是储存电荷的组件,愈大的电容可储存愈多的电荷,因此在看电源路径时,可视电流由电容正端出发,经由开关组件的回路后再回到电容的负端形成开关回路。

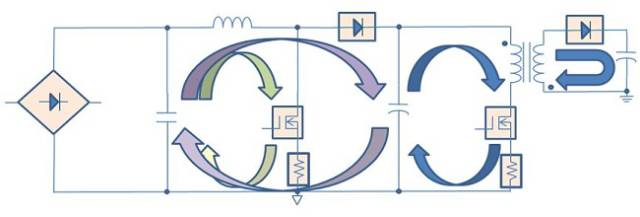

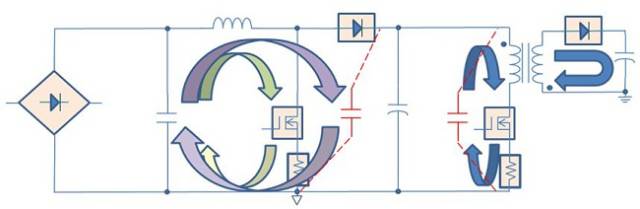

图20为一升压加反激(PFC+Flyback)架构的例子,PFC前端会有一颗小电容,PFC会由此电容形成一导通回路(绿色箭头)经电感,MOSFET,Rsense回小电容,与截止回路(紫色箭头)经电感,二极管,大电容回小电容;即电流由电容的正端出发,经一回路之后再回到电容的负端;

同理,Flyback由大电容的正端开始,经变压器,MOSFET,Rsense后再回到大电容负端;输出则由变压器的正端,经输出二极管,输出电容后回到变压器的负端。

图20

因电源路径有很大的电流与电压变动,因此在布线时要注意,流过大电流的回路会产生磁场辐射,因此大电流的走线要尽量短与粗,尤其是次级侧。

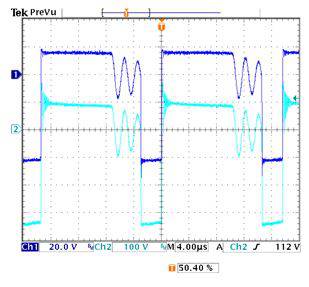

高电压开关的走线则要尽量减少其面积以减少电场效应,并尽量减少其相临的导体面积与之间的距离以减少等效电容,图21与22为量测反激式变压器两端的电压波形,由波形可知在MOSFET的Drain端与Diode的正端有很大的电压变化量,因此在布线时此两点的布线面积要尽可能的小,也尽量远离其他的导体以避免电场效应。

图21

图22

有时因为布线的考虑,无法将回路变的很短,这时我们可以靠高频电容来帮忙,像是在大电解电容同电位上并联一个陶质(高频)电容,因多数的电解电容是低频组件,而并联的高频电容可以提供开关时的高频电流,此电容可放在如图23所示的位置。

在PFC端可在二极管后端并一颗小电容且靠近PFC MOSFET的地,缩短PFC截止时的回路,而Flyback端则可以在靠近变压器正与Rsense负端并一颗电容来形成较短的回路;愈短的回路可以减少电场导体与磁场回路的面积来得到更好的EMI效果。

图23

5.2.2 信号路径的基本概念

凡不是电源路径(Power trace),皆可称为信号路径(Signal trace),因IC是撷取电源路径里的电压/电流信号来维持系统的稳定,因此在信号路径里最重要的就是从撷取信号源到各IC 脚端时是否干净以利IC运作。

在电磁干扰的领域里,信号路径一般需注意两点,一是辅助绕组(Vcc)回路,一是小信号回路。

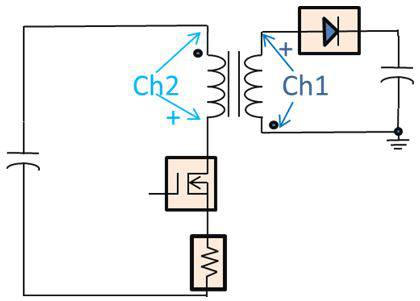

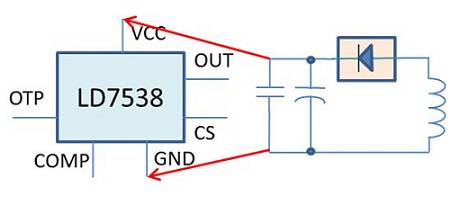

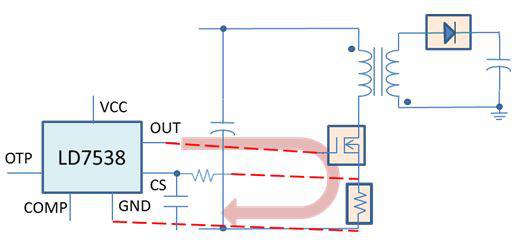

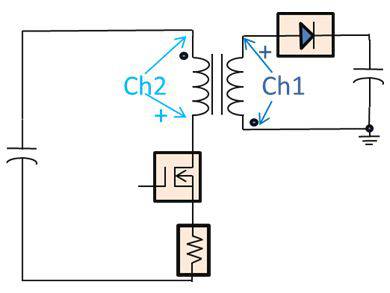

辅助绕组回路如图24所示,在此举例的IC为通嘉的6 PIN IC(LD7538),其辅助绕组回路是由变压器的辅助绕组绕组,二极管,电解电容先形成一开关回路再接至IC,就如同二次侧的切换回路一般,让此开关回路越短越好。

IC的供电脚与地脚旁边通常需并联一颗MLCC小电容(0.1uF),此电容越近IC越好,因此电容是高频电容,IC在驱动MOSFET时会由此电容抽能量,且其他噪声在进IC前可先被此电容过滤一次,不论此噪声是经由偏压回路或是地的回路皆有过滤作用。

图24 小信号回路是指IC的各个出脚端,信号愈小的脚位愈容易被干扰,IC在运作时不外乎侦测电压或电流信号,电压信号是由此脚位与地之间形成的电压准位来做判定,而电流信号则是由撷取信号端到IC脚位上的电流大小来决定,因信号愈小愈容易被外来的信号所干扰,尤其是不到1V的电压信号或是不到1mA的电流信号,所以在布线时要非常小心此小信号的走线。

另外,IC驱动MOSFET的栅极回路里也会回到IC的地而形成一电源回路,因为了减少开关损失,IC流入或流出MOSFET的栅极电流有时会超过1A以上,因此IC的输出至MOSFET的栅极与IC至地的走线也很重要,其回路就如同下图粉红色所示。

在此以反激式架构来做说明,反激式简图如图25所示,MOSFET下方会串联一电阻(Rsense)来做电流侦测,其侦测的信号通常都很小来达到低功率损失(<1V),因此布线时要注意此电阻正端截取的信号线,若此信号线在回IC前有加电阻与电容的低通滤波器(RC filter)。

则此电阻电容要愈靠近IC愈好,如此可让任何外来的噪声在进IC前皆被此滤波器衰减过,而电阻的负端(GND)回IC的路径也是愈短愈粗愈好,因IC是侦测电阻两端的电压来运作,路径愈短可以减少寄生电感的效应而让IC看到愈真实的信号。

图25

因IC的信号一般都较小,很容易受到外来的干扰而产生误动作,因此在布线时除了要注意与电源路径的距离外,也需注意与任何会产生干扰的组件,像是与磁性组件的磁力线会影响到的周边,或是电源输入线材周边等高压电位都是需注意的地方。

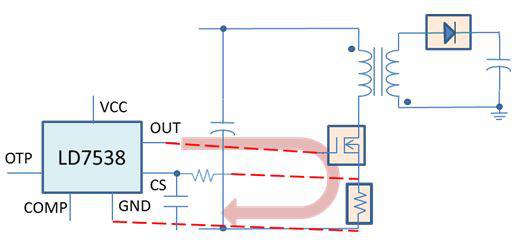

电源与信号路径有一个共同接点:GND,地的走线对EMI影响非常大,参考的地回路接线方式如图26所示。

图26

橙色线为Y电容建议连接法,让输出的地经由Y电容直接连至桥式整流器的负端,让雷击或ESD的能量可以快速的经由Y电容通过。

绿色线为辅助回路的建议接法,让电解电容直接回变压器的地,再单独接至大电容的地。

红色部份为IC的地建议接法,因MOSFET下方的电阻是电源路径(会走大电流),要尽量的靠近大电容来形成较小的电流回路,再由大电容拉一条线至辅助绕组的积层陶瓷电容(MLCC),再进入IC的地。

而其他IC周边组件的地,即以MLCC电容为中心连接点,此接法一般称为心脏接地,即以此电容为心脏中心,IC周边下地点都接回至此电容,如此任何的地信号要进入IC的地之前,都可以先被此MLCC电容过滤成较干净的信号。

在布线时,任何大面积的导体都需要特别留意,包括散热片/外壳/输入/输出线材等,这些导体如同一天线,会放大任何在上面的信号,不但这些组件所接的位置非常重要,其经过的路径也需注意;

一般来说,散热片与外壳不可空接,否则其很容易与周边组件耦合电场效应而产生高频干扰,一般会使其接一较干净,在运作时不会有电位差的电位(GND)。

在此建议的布线方式并不是最好的方式,因不同的变压器设计与布线不同,在EMI里的结果也会有差异,有时必需将干扰源抑制在二次侧或初级侧,有时则必需将干扰源由Y电容或其他组件导出以得到较佳的EMI,因此在此只提出一个布线的设计参考,使用者在对策EMI时仍需做不同的布线方式来得到最佳的EMI效果。

06 EMI滤波器设计概念

6.1 基本概念

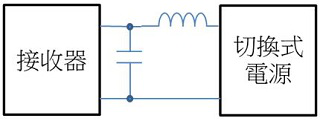

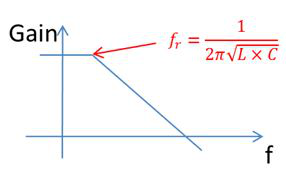

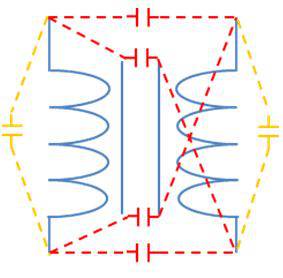

在开关电源的设计里,为了对策传导干扰大都会在输入端前端加入EMI滤波器,因传导测试是由AC端来做量测,因此滤波器愈靠近接收器效果愈好(让所有的干扰都可经由滤波器做衰减),而一般滤波器是经由电感与电容组合而成的二阶低通滤波器。

如图27所示,当干扰信号在经过接收器之前,由电感与电容组成的二阶低通滤波器来衰减高频信号,由图28可知,愈大的滤波电感或电容,可以让谐振频率点往前移而衰减更多高频信号。

图27

图28

6.2 耦合路径

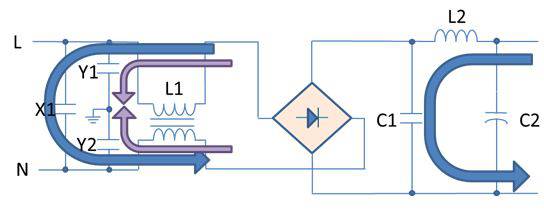

在滤波器设计上,需确认要衰减的路径是差模还是共模,如图29所示为常用的EMI滤波电路,蓝色回路为差模滤波器,左边为L1与X1,右边则由L2与C1所组合而成的差模低通滤波器,紫色回路则为共模滤波器,分别由上端的L1与Y1,L1与Y2组合而成。

图29

6.3 实际的滤波器考虑

理想的滤波器很容易理解,高频干扰经过低通滤波后衰减其高频信号。但在实际应用里,电感或电容愈大,有时并不一定有较好的EMI效果,甚至有时还会较差,这是为什么?

因真实的电感或电容,必需考虑到组件内部的等效电路,像是理想的电容,其阻抗会随着频率增加而减少,但在实际的电容器内部会有ESL与ESR,当频率与阻抗曲线在超过自谐振频率点(Fr)之后,其阻抗反而会因ESL的效应而导致频率愈高,阻抗愈大。

下面就对滤波电感与电容个别来做介绍:

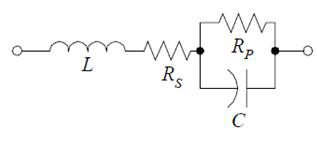

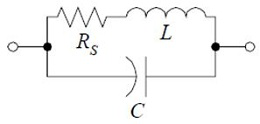

电容:图30为一电容的等效电路,L为等效电感,Rs为等效串联电阻,Rp为等效并联电阻,C为其电容值

图30

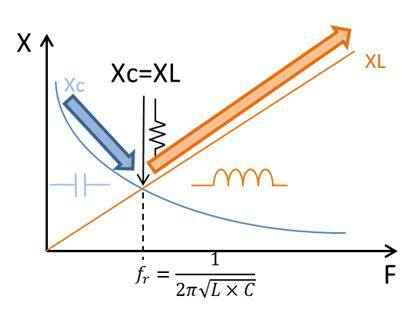

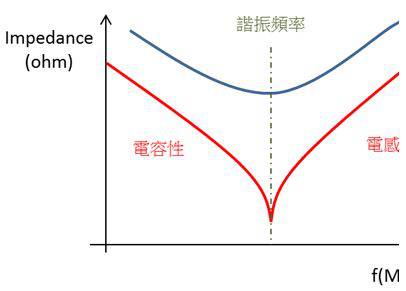

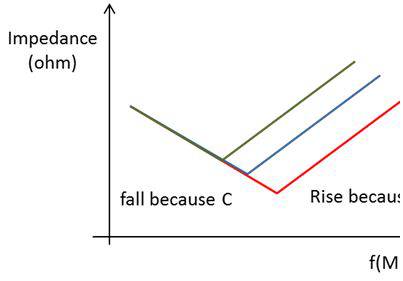

实际的电容器除了电容值外,仍必需考虑其等效电感与等效电阻的影响,其特性曲线如下图所示,电容的XL是由其内部的ESL所造成,因电容是由二片金属板绕制而成,因此容值愈大,其ESL也会愈大,也因此Fr也会在愈前面,当频率过了Fr后,其阻抗会由电容性改为电感性。

由图31的阻抗等效图可以看出,电容器在低频时,确实是由电容所主导,频率增加而阻抗降低,但在过了Fr后,阻抗特性开始由电感(ESL)所主导,频率增加后阻抗反而会上升,在此频段的电容呈现一个电感的特性。

图31

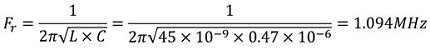

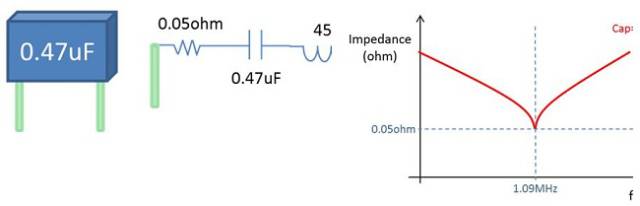

在此举例一0.47uF的X电容如下图32所示,左边为其外型与等效内部电路,右边则为等效内部阻抗与频率曲线图,量测得知其等效电感为0.45nH, 等效电阻为0.05ohm,我们可以看出其阻抗在1.09MHz之前是呈电容性下降,在1.09MHz时呈现急速下降至ESR的位置,并在1.09MHz后呈现电感性上升,转折频率点为

与图中转折点相同(此图为示意图,详细曲线图请确认电容器厂商规格书或用LCR设备量测)。

图32

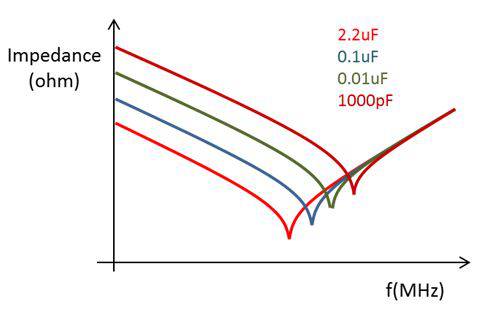

所有的电容其实都有此频率特性曲线,像是图33为一相同类型但不同容质所得出的阻抗与频率曲线,由此图形可知,不同的容质会因其容质与ESL不同而有不同的共振频率点与与频率曲线。

图33

一样MLCC的电容,也会因为其介电系数的不同而影响阻抗特性曲线,如图34所示为Z5U与NPO(相同容值)所呈现出来的阻抗与频率曲线。

另外,相同材质与容质,也会因不同的包装影响其ESL而有不同的阻抗特性曲线,如图35为相同容值与材质,但包装不同(0402/0603/0805)所呈现出来的阻抗与频率曲线。

图34

图35

由上面的阻抗与频率特性曲线可得知,在对策不同频段的电磁干扰时,必须考虑不同材质,不同包装的电容在此频段时的阻抗特性为何,并依此来选择电容器才能达到预期的效果。

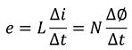

电感:图36为电感的等效电路,Rs为等效电阻,C为等效电容,L则为其电感量。

图36

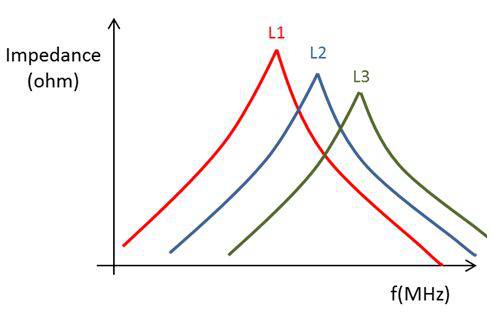

与电容器相似,其频率特性曲线如图37所示,在转折频率点以下时是由电感所主导,但过了转折频率点之后,会由电感的等效电容主导,当频率愈高时阻抗反而愈小。感量愈大的电感,因其必需绕制更多圈数来得到其所需的感量,因此更多的圈数会导至更大的寄生电容,转折频率点也会较为前面。

而在高频时的衰减能力也会较差,如图38所示为三颗相同环形铁心绕制不同圈数后得出的阻抗频率特性曲线,L1最多圈因此在前频段时上升最快,但也因寄生电容最大而最快被衰减。

另外,电感的等效电容与电感的绕法/圈数有很大的关系,一般是圈数愈多会有愈大的等效电容,但电感的绕制可以用绕法的不同,像是十字绕法,蝴蝶绕法…等方式,用相同的电感但不同的绕法来得到相同感量但减少其等效电容,藉此来得到较佳的EMI效果。

图37

图38

07 变压器在传导的设计概念 一般工程师对变压器的观念,就是用铜线在铁粉心的铁心上绕线,并根据不同的圈数与感量,可得到不同的工作周期,电流变化率与MOSFET/DIODE的电压应力;但在EMI的领域里,变压器的设计就没有这么简单,经验丰富的工程师都知道良好的变压器设计在EMI里占有举足轻重的地位,下面就一一来介绍:

7.1 变压器的基本概念

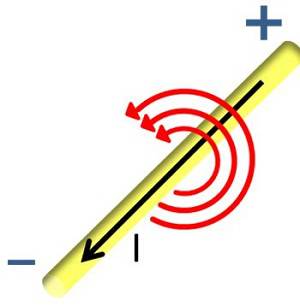

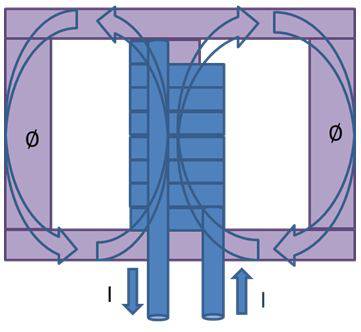

一般开关电源的变压器皆是使用铁粉心(Ferrite Core)制成其铁心,再由线圈绕制在铁心上而成,以图39左边所示为一线圈绕制在铁心中间时,因电流在铁心里所产生的磁通方向。

图39

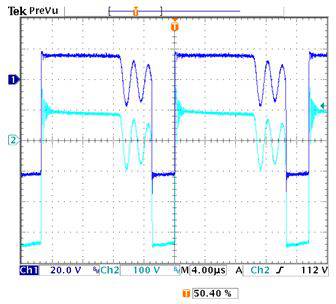

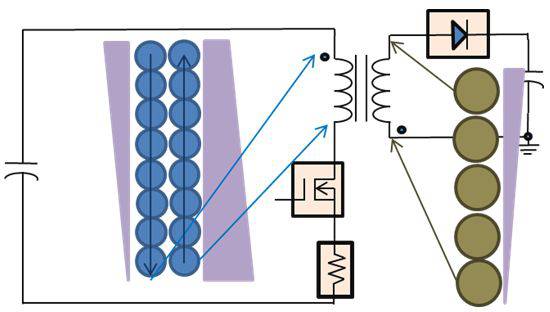

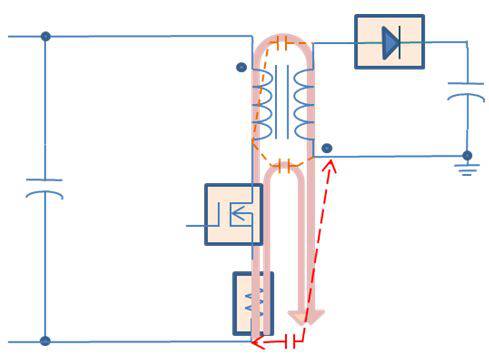

如图40与41简易的反激式线路图与波形,此为一65W在230V输入时的工作情形,量测变压器初级与次级侧(如图所示探棒位置),因开关电源是靠开关做快速开关来得到稳定的输出,当MOSFET开关关断时,初级开关的Drain pin会由低电压提升至高电压,同时次级二极管端也会同样的由低压至高压。

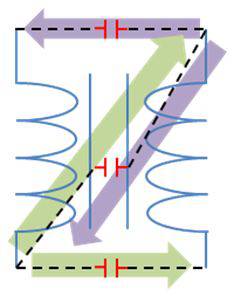

但初级侧电压的电位差会远高于次级侧电压,由之前的观念可知道,两导体之间会有耦合电容,而此电容会因电位差而产生一电流,如图42所示,当初级侧导体的电压高于次级侧时,将会有一电流由初级侧导体经由耦合电容流入次级侧(如绿色箭头);

同理,当开关导通时,初级与次级导体的电压会由高电压降低至低电压,由于初级侧的电位差比次级侧较大,因此这时也会有一电流由次级侧导体流入初级侧(如紫色箭头)。

图40

图41

图42

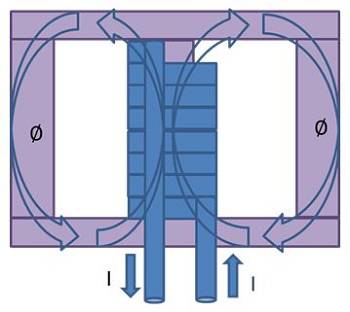

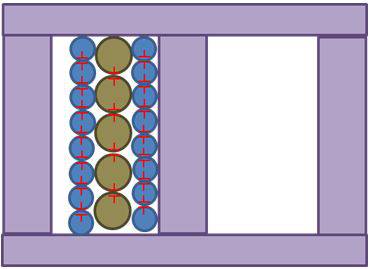

在成型的变压器铁心内部会有多数铜线绕制而成,其结构图如图43所示,此为一三明治绕法的变压器,紫色为变压器铁心,蓝色为初级侧铜线,棕色为二次侧铜线,绕制顺序为:最内层由MOSFET的Drain pin开始由下往上绕,接着再绕二次侧,最后再接着初级的线圈由上往下绕下来,达成三明治绕法(将二次侧夹在内层),但初级导体与次级导体之间因距离很靠近,所以在两者之间会有耦合电容的产生,就如红色电容所示。

由刚才的波形可得知,MOSFET的Drain pin与二极管的A端是电压变动率最大的地方,而变压器线圈的另一边是静点(因直接连接电容,电压无法瞬间变化),所以内部线圈的电位差是由变化量最大的一端往另一端减小,就如图44紫色所标示一样,线圈愈靠近MOSFET的Drain pin或是二极管的A端有较大的电位差,而电位差的变动量随着往另一端愈近而愈小。

图43

图44

因此在实际的变压器绕制上,都会建议变压器最内层是由电位差变化最大的点开始起绕,让愈外层的铜线其电位差愈小,如此可让最内层高压变化的电场被其他相对电位较小的导体包覆在里面来减低其对外的辐射效应。

另外,在做变压器设计时,若一开始就可以考虑此因绕组电位差所导致的电场效应,将可大大地减少EMI除错时间。

除了介于初级与次级侧之间的层间电容之外,初级侧本身与次级侧本身之间也会存在着耦合电容如图45红色所示,而在变压器线路里其等效的寄生电容如图46所示,红色为介于初级与次级之间,黄色则为初级本身与次级本身。此电容量会随着圈数的增加而上升,而此电容量也会引起高频电场干扰。

图45

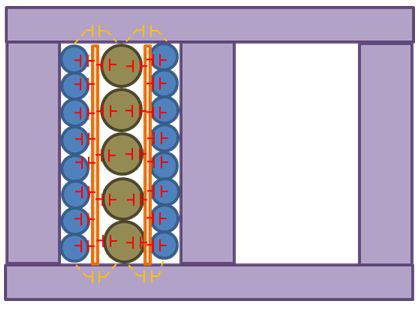

图46 7.2 内铜

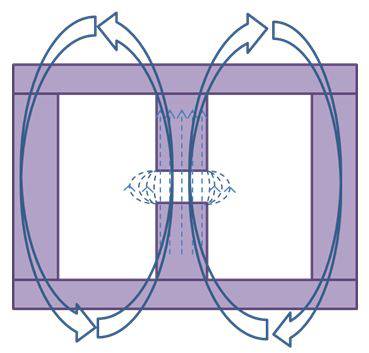

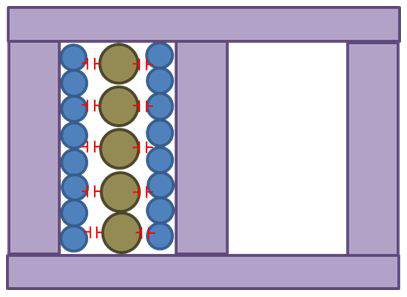

因介于变压器初级侧与次级侧的耦合电容会引起严重的电场干扰,因此一般会在初级侧与次级侧之间做电场隔离来减少电场效应,一般使用的方式是在初级与次级之间加一层内铜箔或是铜线做电场隔离,如图47所示为加了铜箔的变压器,内铜箔介在初级与次级之间,由高电位差引起的耦合电流大部份会经过红色的耦合电容至铜箔而形成另一个回路,大大地减少了耦合至另一侧的耦合电容。

若将此铜箔下PIN回初级侧(可以是地或是高压),相当于初级侧产生的高电位差,经由电容效应到铜箔上,再经由铜箔回到初级侧本身,形成一初级侧的电流回路,帮助初级侧电场电流回到初级侧而做到电场隔离;如此只剩下少部分的如图48黄色的耦合电容,大大地减少电容效应来达到减少电场干扰的作用。

图47

图48

7.3 Y电容

一般在变压器的初级与次级侧,我们都会在两端的地之间放一颗Y电容,而此Y电容的作用也与上述的一二次侧耦合电容相关;如图49线路所示,红色的Y电容介在初次级侧之间,而初级侧电压变动所导致的电容效应,即耦合至次级侧的电流,可以多了一个路径,即经由此Y电容回到初级侧,大大的减少共模路径的干扰。(若没有此Y电容,则大部份的耦合电流都会经由大地FG回至初级侧)

也因为Y电容是给予初级次级侧一路径,因此连接的位置与大小也很重要,电容Xc的阻抗为1/2*π*f*c,代表频率愈高时,其阻抗愈低,高频信号愈可以由Y电容流入另一侧,但决定的因素却是因变压器与布线不同而有不同差异,因对策有时需将干扰源留在内部较好,有时却是将其流入外部较好,因此不同的案子都必需对Y电容做些调整。

图49

7.4 漏磁

变压器的漏感(漏磁通)不但会造成初级侧开关Vds过高,也会对EMI产生很大的影响。

一般开关变压器的铁粉心里都没有气隙,因此实际使用时都会因饱和问题而将铁心磨气隙,而漏磁最大的地方就在气隙周边,在设计时要尽量选择将气隙放在变压器内部中心处的铁心,再用导体或铜箔做屏敝来减低其漏磁的影响,而气隙中间的漏磁通如图50虚线所示。

除了气隙外,虽大部份的磁通会经由导磁路径(即变压器铁心)形成一回路,但仍会有些许漏磁会在变压器外部形成漏磁通,此漏磁通如图50蓝色箭头所示,漏磁产生的磁场干扰很容易会影响周围的导体或组件。而减少干扰的方法,一是对变压器进行磁场屏蔽,另一是尽量拉开与变压器漏磁通之间的距离,或尽量减少在其周边的电流导体面积。

图50

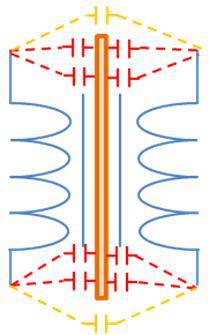

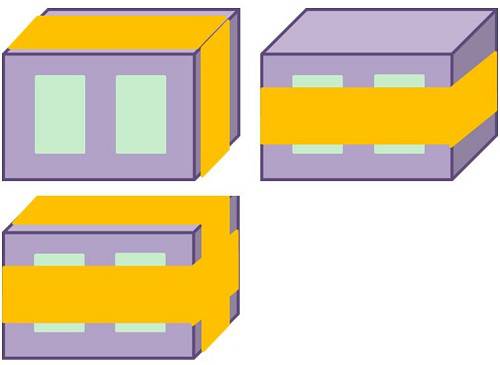

7.5 外铜箔

所谓的外铜箔是在变压器铁心外围包覆一铜箔,包覆方式可延着铁心包覆或是延着线包包覆,也可以同时包覆铁心与线包(十字包法),简易如图51所示,左边为铁心包覆,中间为线包包覆,右边则为十字包法,而铜箔两端接触后需相连并下地,如此不但可作电场屏蔽也可作磁场屏蔽。

非导磁材料一般是无法对磁通有屏蔽作用的,但铜箔是良导体,漏磁通穿过铜箔时会产生涡流,而涡流产生的磁场正好可抵消变压器的漏磁通,如此来抑制漏磁所造成的磁场干扰。而铜箔的良导体特性也会抑制电场耦合效应,就如内铜箔的作用一样。

图51 08 对策EMI——传导的方法

在做传导测试时,可先依下面做些确认。

8.1 确认测试方式

首先必须确认测试方式是否正确,不正确的测试方式会浪费很多时间,确认的地方包括测试法规为何/测试电压为何(不同国家有不同电压输入)/待测物是系统或是仿真负载/系统的工作模式(是否过载或动态负载)/系统的周边(monitor,USB或硬盘)是否会造成干扰源/输出或电源线是否需下地/外接设备的地线是否与主电源的地线有分开/是否先空扫一次确认接收器的误差…等等;

建议在开始对策之前,先确认以上的测试环境是否正确,再开始做对策;笔者就有过对策一个下午后,才发现其中一项设定错误,白白浪费一个下午时间的经验。

8.2 确认导体的天线效应

任何的导体在测试EMI时都会有天线效应,因此建议使用客户量产所用的线材,包括输入线材与输出线材(不同的线材会有些许的差异),而散热片一般会下地(或一参考电位),外面有铝壳或金属导体时也要下地,避免导体因电场或磁场效应而产生干扰,成品的组件组装上也需注意是否有远离干扰源,任何导体经过磁性组件周边时也要注意磁性组件漏磁通所带来的干扰。

8.3 在150KHz~10MHz的频段一般是由操作频率的倍频差模信号加上共模信号所组成,一般对策方式为修改EMI低通滤波器/变压器耦合路径/Y电容大小/布线方式等来做对策,可依文章前面所述方法做确认。

09 结 语 电磁干扰(EMI)的防制在电源设计里是门很重要的学问,此篇文章将EMI传导的法规,量测法做介绍,并解释传导的一些基本概念,包括电场干扰与磁场干扰等,并分析布线,EMI滤波器与变压器设计对EMI的干扰等。

所有的EMI问题,其实皆因高速的电压变动所产生的电场干扰,或是高速的电流变动所产生的磁场干扰,并搭配组件或布线的高频路径(包括寄生电感与电容)所产生,因此只要知道开关电源的电场与磁场来源,并知道各组件内部的等效电路与布线路径,就可以知道用怎样的方式可得到较佳的EMI结果。

![]()