RISC-V 指令集架构旨在提高软件跨不同应用程序和平台的可重用性。现代片上系统 (SoC) 平台具有数十种指令集架构,可满足市场需求。其中包括应用程序、图形、成像、无线电 DSP、音频、安全、电源管理和专有指令集处理器。RISC-V 开源指令架构提供了一个免费和开放的指令架构,可以满足大部分这些需求。为了设计复杂的架构,需要一个系统级建模平台,该平台具有一个全面的总线、存储器和外围 IP 块库。该环境必须模拟和分析电源、时序、调度和功能的非功能性需求。

现代 SoC 具有以不同时钟速度和硬件加速器组合运行的变化。这些 SoC 的复杂性使得使用分析方法进行测试不准确,使用 Verilog/VHDL 进行验证也不切实际。使用编程语言的解决方案需要投入大量精力来开发所有必需的 IP 块,然后将它们集成到一个平台中。使用指令集模拟器可以帮助进行早期软件开发。但是这些模型过于抽象,无法提供系统操作的真实视图。

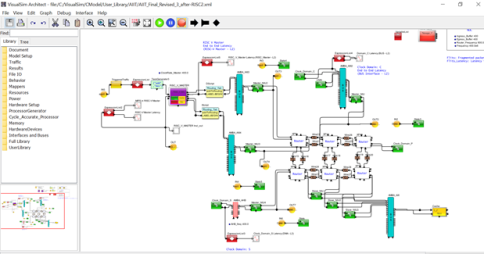

图形离散事件模拟器是探索和验证 RISC-V SoC 架构的绝佳解决方案。Mirabilis Design 的 VisualSim Architect 就是这样一种软件包,它提供了一个大型的现成组件库,可用于组装系统模型。其中包括 DDR3/4/5、LPDDR、以太网、RapidIO、PCIe、FibreChannel、缓存、DMA、AMBA、NoC 和 40 种其他技术。VisualSim 等工具用于模拟高性能计算、多媒体、航空电子设备、汽车、网络和物联网中的 SoC 和系统。在 VisualSim 中组装模型后,设计人员可以对硬件-软件分区、软件任务调度、拓扑选择、资源分配和电源管理进行试验。使用仿真模型,所提出的架构将被定量测量、分析、和回归测试,而不是以前设计的猜测和提示。使用各种用例、工作负载以及拓扑、外设、I/O、存储器和 DMA 的组合来模拟生成的模型。多核 RISC-V 将以网格和 NoC 拓扑部署,用于不同的目标活动。在设计阶段早期缺乏一组固定的应用程序,因此很难预测性能。在 VisualSim 的情况下,可以使用指令序列或延迟值来模拟软件。这些是根据配置文件统计生成的。多核 RISC-V 将以网格和 NoC 拓扑部署,用于不同的目标活动。在设计阶段早期缺乏一组固定的应用程序,因此很难预测性能。在 VisualSim 的情况下,可以使用指令序列或延迟值来模拟软件。这些是根据配置文件统计生成的。多核 RISC-V 将以网格和 NoC 拓扑部署,用于不同的目标活动。在设计阶段早期缺乏一组固定的应用程序,因此很难预测性能。在 VisualSim 的情况下,可以使用指令序列或延迟值来模拟软件。这些是根据配置文件统计生成的。

使用 VisualSim Architect 对监控 SoC 进行架构探索

RISC-V 架构

在本文中,我们考虑使用 16 核 RISC-V 架构的高性能计算设计。为了研究这种架构,我们使用了 RISC-V 内核的 VisualSim 混合流水线模型,具有乱序行为、缓存、指令集和执行单元。用户可以定义 iCache、dCache、L2(外部或内部)、交叉开关、可选 L3 和外部存储器的任何配置。该模型可以通过发送不同的指令序列来模拟,以验证候选架构的性能。可以修改模型参数以选择正确的内存结构以保持管道繁忙。在尝试预取指令或数据时,将测试缓存/内存大小和配置是否存在瓶颈。VisualSim 模型将识别处理器模块的系统停顿统计信息。

现代 SoC 架构的一个主要考虑因素是显着的节能。提议的 RISC-V 平台将展示一个端到端的电力系统,包括发电、存储(电池)、消耗和管理。将对各种管理算法、路由表、无线信道和电池类型的功率影响进行研究。

使用系统级设计最重要的方面是能够查看处理器的外部活动,并在需要时改进外部硬件加速器、内存通道、总线结构、宽度、速度等。该模型有助于设计师可以深入了解许多已知和未知用户应用的处理器性能-功率组合。系统级别的行为分析评估性能、功率和功能正确性。结合所有三个分析标准对于做出任何架构决策和提供对整个系统操作的可见性都是必不可少的。

系统级探索和分析的主要关注领域是:

新设计:新平台的设计需要从更低的价格、最高的性能和最低的功耗方面来探索架构。如果在实施过程中早期的假设被证明是不正确的,项目进度将会出现重大延误。例如,构建了双 RISC-V 设计,并且总线太慢或需要修改内存层次结构,这将导致视频传输速度显着下降。我们将查看我们内部开发的最新设计,以比较双 RISC-V 与 ARM Cortex M4 处理器拓扑。

向现有平台添加新应用程序:系统公司希望在现有硬件平台上使用软件添加新应用程序。当一个新的应用被提出时,仿真模型被用来快速评估当前平台是否支持增量负载。根据这项研究,设计人员可以确定应用程序中需要硬件加速器的部分。

对性能、功率和功能的早期设计探索为新的创新设计理念提供了验证。此外,相同的基础设施可用于系统级验证和营销宣传以赢得设计。

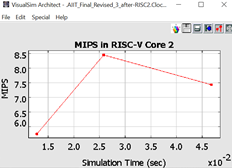

评估 RISC-V 核心处理器效率

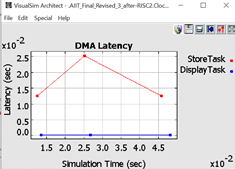

高吞吐量视频数据的传感器到内存延迟

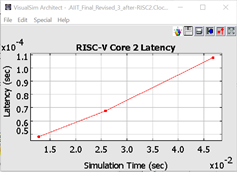

RISC-V 内核上的软件任务延迟

结论

RISC-V 有可能成为从高性能计算到物联网等各种行业的主要颠覆性技术。系统级模型(例如 VisualSim Architect for RISC-V 中的模型)将使设计人员能够快速为其目标应用选择配置。广泛的建模 IP 将使每种类型的 SoC 和系统都能够在目标应用程序中构建和测试。这些实验可以帮助创建能够满足并超过时序要求、消耗最低能量并满足成本因素的 SoC。

![]()