一、基本介绍

1.1 常用SDRAM

SDRAM(Synchronous Dynamic random access memory)即同步动态随机存取存储器。常用SDRAM的种类有SDRAM、DDR1-5、LPDDR2-5。

1.2 容量计算

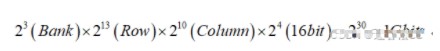

容量(bit)= Bank数×行数×列数×位宽。以Etron品牌的DDR2物料EM68C16CWQD为例,在ERP系统中查到的物料描述“1Gbit | 8Mbit*16Bit*8Banks”。查询Datasheet可知,该DDR2物料容量为1Gbit,包含3根Bank控制线BA0-BA2,13根地址线A0-A12,其中行地址为A0-A12,列地址为A0-A9,数据总线位宽16bits,可以计算出总容量为:

1.3 选型

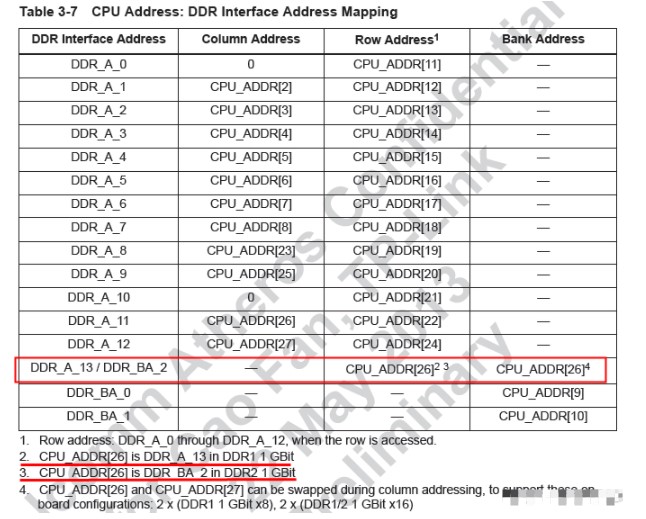

一般根据实际项目需求来选择合适容量的SDRAM,根据主控芯片的接口来选择不同位宽、Bank数的SDRAM,并考虑是否需要进行位扩展。以主芯片为QCA9531,内存需采用1Gbit DDR2。 查询主芯片QCA9531的Datasheet中关于DDR接口部分,可以了解到QCA9531支持16bit位宽,并且在外接1Gbits DDR1时,A13作为行地址的最高位,外接1Gbits DDR2时,A13引脚作为Bank地址线BA2。所以,连接1Gbit DDR2时,主芯片可以提供13根地址线和3根Bank线,与DDR2物料EM68C16CWQD可正常连接使用,并且不需进行位扩展。主芯片QCA9531的DDR接口说明如图1所示:

位扩展主要在主芯片位宽高于内存芯片位宽的机型上可以看到,即主芯片外挂多个内存芯片,共用地址线,扩展数据线。

二、原理图设计

2.1 合理端接

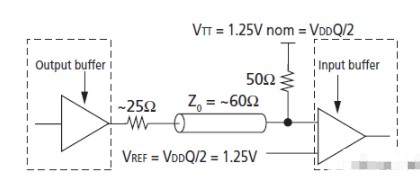

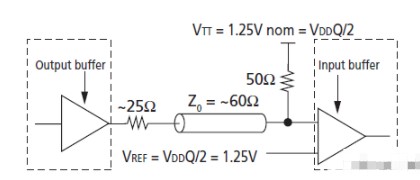

当信号的上升/下降时间足够小,或者信号频率足够大时,在阻抗不连续处发生的信号反射可能严重影响信号质量,需要考虑信号完整性的问题。可以把DDR走线按传输线的理论来分析,需要在走线上实现阻抗匹配以消除反射,尽量保证信号完整性。常见的DDR电路匹配模型是源端串联,终端并联,即在靠近驱动端的输出引脚串联电阻实现源端匹配,在靠近接收端的输入引脚并联电阻实现负载端匹配。常见的端接拓扑如图2所示:

源端串联,终端并联的方式优点是反射小,但缺点是外围器件多,占用PCB空间大,SOHO产品线基本没采用这种匹配方式,而是在走线上只放置一个串联电阻。由于PCB尺寸有限,并且芯片封装尺寸较小,串联电阻只能是尽量靠近驱动端放置,尽可能地减小源端反射。考虑到DDR数据是双向信号,写信号的驱动端是主芯片,读信号的驱动端是内存芯片。串联电阻靠近主芯片放置,还是靠近内存芯片放置,还是放置在走线中间,也是需要权衡的问题。一般情况下,考虑主芯片和内存芯片哪个的驱动强度大,串联电阻应靠近驱动强度大的芯片那端放置。

2.2 数据线交叉连接

一般情况下,在最初的原理图设计中,主芯片与内存芯片的数据线是按一定的顺序连接起来,以位宽为8bit的情况为例,主芯片D0~D7按顺序连接到内存芯片的D0~D7。但是,在Layout过程中,如果遇到DDR数据线在PCB上出现交叉的情况,可以修改原理图,让数据线交叉连接,例如,将主芯片DQ0、DQ3与内存芯片DQ3、DQ0连接,使得PCB Layout的时候走线就更加顺畅。

2.3 预留调试器件

重要的走线上预留一些调试手段,在后续的样机调试上有一定的作用。例如可以在差分时钟线上各加一个并联到地的电容,在差分线之间加入并联电阻,在DQS上加并联到地的电容。

![]()