据韩媒报道,近日,三星电子AVP先进封装部门正在开发面向AI半导体芯片的新型“3.3D”先进封装技术,目标2026年第二季度实现量产。

(图源:ETNews)

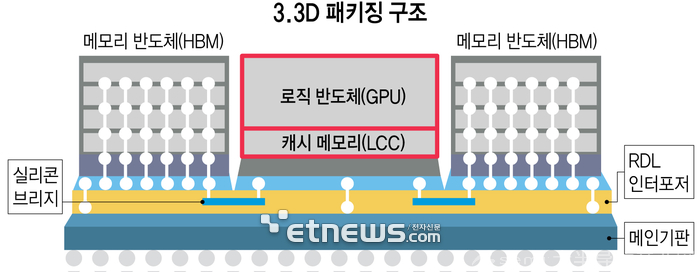

据悉,三星电子正在开发一种技术,通过安装“RDL中介层”而不是硅中介层来连接逻辑芯片和HBM。使用RDL中介层代替硅可以将材料成本降低十分之一,为了让性能下降最小化,可以仅在必要的部分(桥接器)中使用硅。

三星正试图更进一步,同时实施3D堆叠技术,将逻辑芯片堆叠在计算所需的LLC之上,三星将其命名为“3.3D封装”。

据称,三星还将在其3.3D封装中引入“面板级封装(PLP)”技术。PLP可以通过将芯片封装在方形面板而不是圆形晶圆中来显著提高半导体生产率。

![]()