PCB 布局和参考回流路径的设计在电路的 EMC 性能中都是至关重要的因素,且对于电源转换电路来说尤其重要。因此设计初期将回流路径可视化是重要的一个环节,通过将回流路径可视化,可以辅助设计和控制整个回路的区域。

图1:单层飞线连接GND

在两层板中,相对于单层板具有更多的优势,因为层与层之间走线可以由过孔连接,并优化回路面积。图 2 显示了在顶层和底层通过过孔连接GND,并改善回流路径的示例。

图2两层板示意图

有时在做PCB设计的时候会建议割地处理(例如模拟和数字地),但根据我们的经验,这样做往往会导致额外的EMC问题。

二可视化完整的回流路径

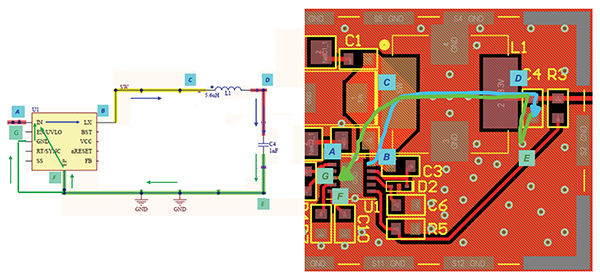

在设计过程中,我们建议将所有电源和信号路径的正向和返回电流分三步绘制。步骤 1:在原理图上绘制的完整的电源路径。第2步:在PCB图上同样绘制电源路径。步骤 3:根据上面两步的结果,优化 PCB 布局和最小化环路面积。

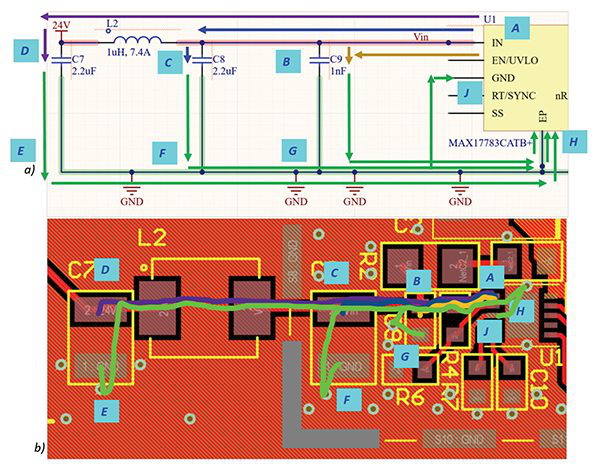

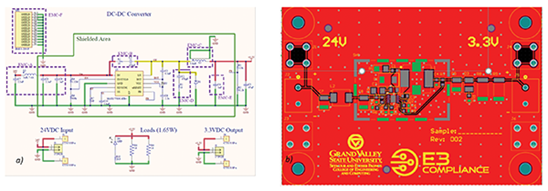

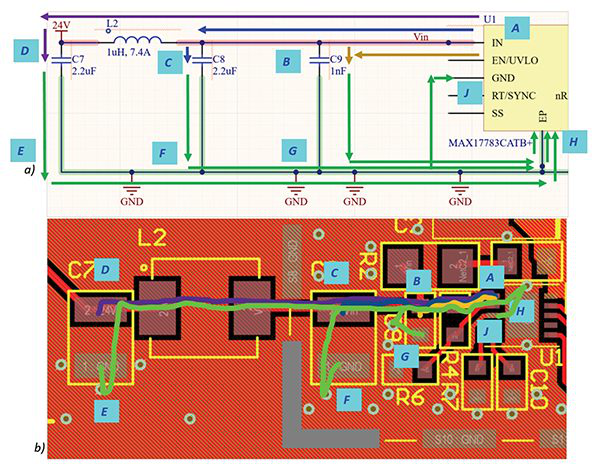

在讨论DC-DC电路设计时,回流路径的设计一直是关注的重点。如图 3 所示,一款DC-DC降压电路的原理图和PCB布局。图 3a:原理图。图 3b:PCB。

图 3:a)原理图 b)PCB

对图3电路可视化回流路径,参考图4。电流的正向路径为ABCD ,电流返回路径为EFG 。

图4:PCB的输出滤波部分

在直流或低频(低于100kHz ),电流会沿着阻值最小的路径返回源端。在较高频率下,回流信号会走感抗最小路径。该感抗由电流的正向和返回路径所形成的环路面积决定。当回流路径直接位于电流正向路径下方时,此时整个环路面积最小,感抗也最小。这意味着如果有完整的地平面,高频电流会直接在正向路径下方的地平面回流到源端,如图 4 所示。

接下来,让我们看看图 5 所示。

图5:DC-DC滤波电路PCB

如图所示,我们假设电流路径从 U1(DC-DC芯片)的 Vin 开始。在这种情况下,高频电流有多个可能的返回路径。高频电流会根据频率不同选择经过C7,C8或C9返回芯片源端,如图5所示。例如,100MHz 的噪声可能会选择通过较小容值的C9回流,而较低频率的噪声(例如 500kHz)可能会选择通过较大容值的 C7 或 C8回流。

三经验法则

为了减少了电流环路面积,并有助于减少开关电源的辐射和传导发射,有以下是几个 EMC 经验法则:

1.在可能的情况下,在信号层底下保持完整的参考平面

2.将去耦和旁路电容尽可能靠近 IC 引脚放置。

3. 高速信号线尽量短,且挨着地线布线,以确保低阻抗路径(最小环路面积)。

4.在内部开关和续流二极管之间放置RC吸收电路,且吸收电路走线尽量短。

5.在开关元件(IC、电感等)下方铺设完整参考平面。

![]()