跳至内容

在上周的 Hot Chips 大会上,IBM 宣布了其新的大型机 Z 处理器。这是一个很有趣的设计,值得大肆讨论一番。但在本文里,我想特别关注该核心设计的一个功能。

IBM Z 处理器以拥有大型 L3 缓存而闻名,并以单独的全局 L4 缓存芯片作为后盾,该芯片可作为多个处理器插槽之间的缓存——IBM 已经通过新的 Telum 芯片取消了这一点——没有 L4,但有趣的是,没有L3。

任何现代处理器都有与其关联的多级缓存。它们由容量、延迟和功耗分开——最靠近执行端口的最快缓存往往很小,然后我们有更大的缓存,速度稍慢,然后可能是在我们到达主内存之前的另一个缓存。缓存的存在是因为 CPU 内核现在想要数据,如果它全部保存在 DRAM 中,那么它每次获取数据将需要 300 多个周期。

现代 CPU 内核会提前预测它需要什么数据,然后先将它从 DRAM 带入其缓存,这样的话内核可以在需要时更快地获取它。一旦缓存线被使用,它通常会从最近的一级缓存 (L1) 被“赶”到下一级缓存 (L2),或者如果 L2 缓存已满,则 L2 中最旧的缓存线将被驱逐到一个L3 缓存以腾出空间。这意味着如果再次需要该数据线,它不会离开内核太远。

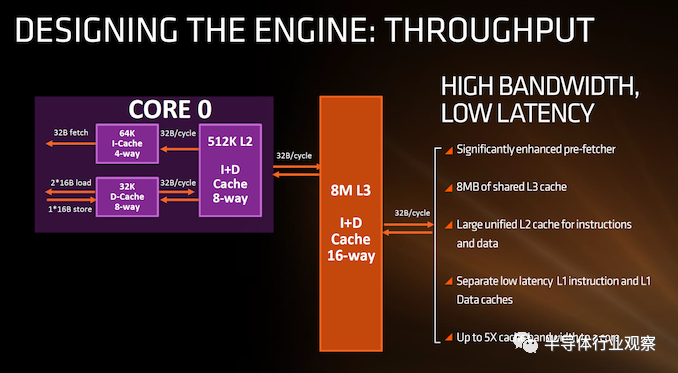

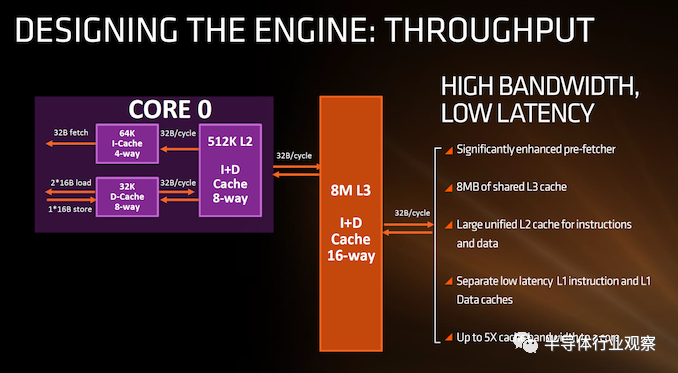

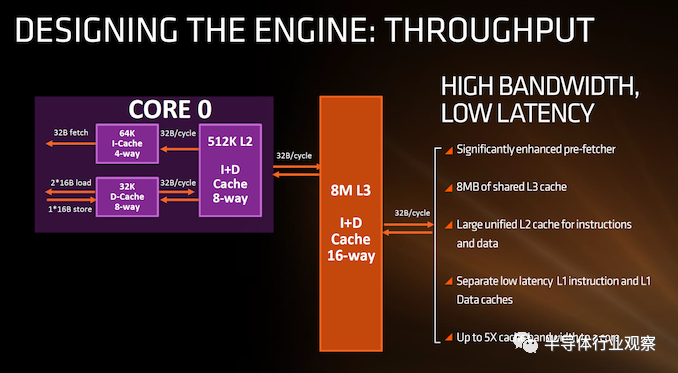

AMD 第一代 Zen 处理器上的 L1、L2 和共享 L3 的展示

现代处理器设计具有多个内核,在这些内核中将至少有一个只有该内核才能访问的私有缓存(L1)。在此之上,缓存可以是仍位于核心本地的私有缓存,也可以是任何核心都可以使用的共享缓存。

例如,英特尔 Coffee Lake 处理器有八个内核,每个内核都有一个 256 KB 的私有 L2 缓存,但在芯片范围内,所有八个内核之间有一个 16 MB 的共享 L3。这意味着,如果单个内核想要,它可以不断地将数据从较小的 L2 赶到较大的 L3 中,并且如果要重用该数据,则可以拥有一个资源池。不仅如此,如果第二个内核也需要一些数据,他们可以在共享的 L3 缓存中找到它,而不必将其写出到主内存并在那里获取。使事情复杂化。最终的结果是缓存有助于减少执行时间,并在需要或需要时从主内存中引入更多数据。

考虑到这一点,您可能会问为什么我们在处理器上看不到 1 GB 的 L1 或 L2 缓存。这是一个完全有效的问题。这里有许多因素在起作用,包括芯片面积、效用和延迟。

芯片面积很容易首先解决——因为最终每个缓存结构可能只有一个定义的空间。当你在硅中设计内核时,可能有一种最好的方法来布置内核的组件以获得最快的关键路径。但是缓存,尤其是L1缓存,必须在靠近需要数据的地方。如果您想要一个大的 128 KB L1 缓存,那么设计与具有 4 KB L1 缓存的芯片布局将会大不相同。所以这里有一个权衡。

除了 L1,L2 缓存有时也是芯片面积的大量消耗者,虽然它(通常)不受其他核心设计的限制,但它仍然必须与需要在芯片上。任何大型共享缓存,无论最终成为 2 级缓存还是 3 级缓存,通常都可能是芯片的最大部分,具体则取决于所使用的工艺节点。

实用性也是一个关键因素——我们在 AnandTech 上主要谈论通用处理器,尤其是那些基于 x86 构建的用于 PC 和服务器的处理器,或者用于智能手机和服务器的 Arm,但是有很多专用设计,它们的作用是针对特定的工作量或任务。如果处理器核心需要做的只是处理数据,例如相机 AI 引擎,那么该工作负载就是一个明确定义的问题。这意味着可以对工作负载进行建模,并且可以优化缓存的大小以提供最佳性能/功耗。

如果缓存的目的是将数据靠近核心,那么任何时候缓存中的数据没有准备好,就称为缓存未命中——任何 CPU 设计的目标都是尽量减少缓存未命中,以换取性能或功率,因此具有明确定义的工作负载,

您拥有的缓存越多,访问所需的时间就越长——不仅因为物理大小(以及与核心的距离),还因为有更多的缓存需要搜寻。例如,可以在短短三个周期内访问小型现代 L1 缓存,而大型现代 L1 缓存可能需要五个周期的延迟。小型 L2 缓存可以低至 8 个周期,而大型 L2 缓存可能有 19 个周期。

缓存设计中涉及到的不仅仅是更大等于更慢,所有大型 CPU 设计公司都将煞费苦心地努力尽可能地缩短这些周期,因为通常 L1 缓存或 L2 缓存中的延迟节省提供良好的性能增益。但最终如果你做得更大,您必须满足这样一个事实,即延迟通常会更大,但您的缓存未命中率(cache miss )会更低。这又回到了上一段讨论定义的工作负载。我们看到像 AMD、英特尔、Arm 等公司与其大客户一起进行广泛的工作负载分析,以了解什么最有效以及他们的核心设计应该如何发展。

在第一段中,我提到IBM Z是他们的大型主机产品——这是行业的大拿。它比政府授权的核掩体建造得更好。这些系统支撑着社会的关键要素,例如基础设施和银行业务。这些系统的停机时间以每年几毫秒为单位,并且它们具有故障安全和故障转移功能——对于金融交易,当它进行时,它必须无故障地提交给所有正确的数据库,甚至在发生故障的情况下整个链条的物理故障。

这就是IBM Z的用武之地。它非常小众,但具有令人难以置信的惊人设计。

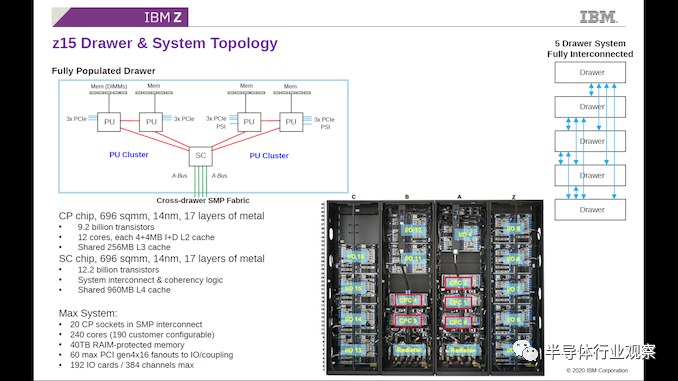

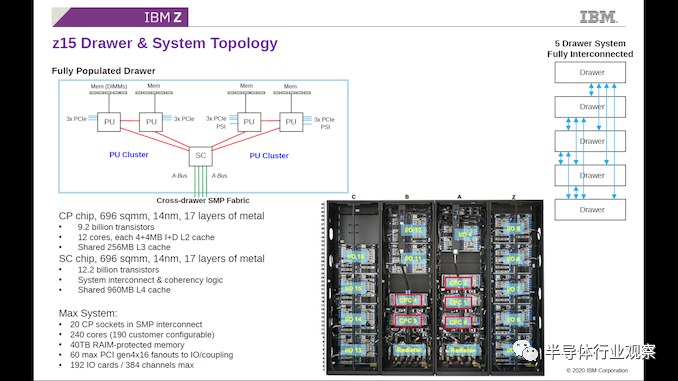

在上一代z15产品中,没有1 CPU = 1系统产品的概念。IBM Z的基本单元是一个五处理器系统,使用两种不同类型的处理器。四个计算处理器 (CP) 每个在 696mm2中包含12个内核和256MB共享L3缓存,构建在14nm工艺上,运行频率为5.2GHz。这四个处理器分成两对,但两对也连接到存储控制器 (Storage Controller:SC),同样是 696mm2和14nm,但是这个存储控制器拥有960MB的共享L4缓存,用于所有四个处理器之间的数据。

请注意,该系统没有“全局”DRAM,每个计算处理器都有自己的 DDR 支持的等效内存。IBM 然后将这五个处理器“drawer”与其他四个处理器组合成一个系统。这意味着单个 IBM z15 系统是 25 x 696mm 2的硅片面积,它们之间有 20 x 256 MB 的 L3 缓存,还有 5 x 960 MB 的 L4 缓存,以全对全拓扑连接。

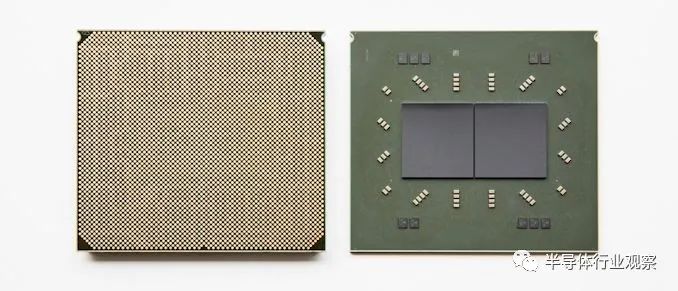

可以说,IBM z15 是一头野兽。但是下一代 IBM Z,称为 IBM Telum 而不是 IBM z16,可能是因为他们对所有缓存采用了不同的方法。

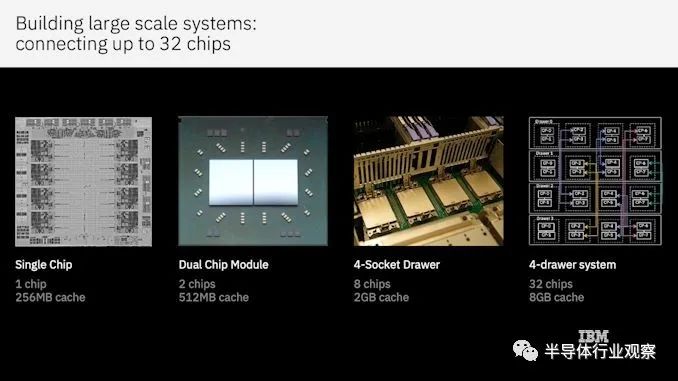

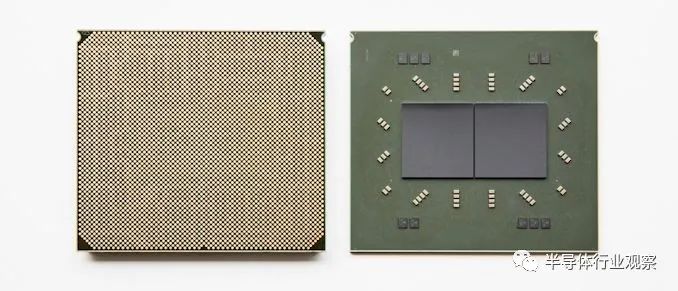

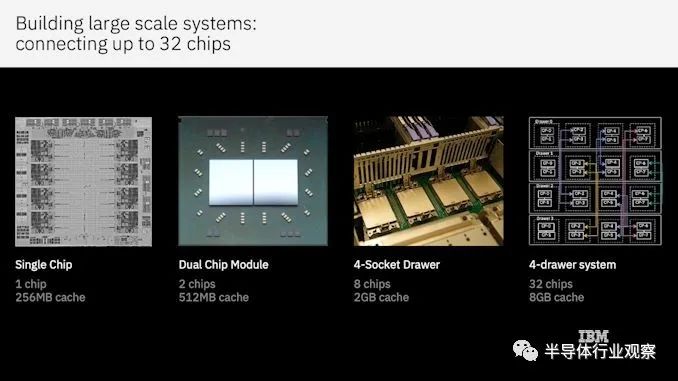

新系统取消了带有 L4 缓存的单独存储控制器。相反,我们有一个看起来像八核的普通处理器。基于三星 7nm 和 530mm2构建,IBM 将两个处理器封装在一起,然后将四个封装(8 个 CPU,64 核)集成到一个单元中。四个单元构成一个系统,总共 32 个 CPU/256 个内核。

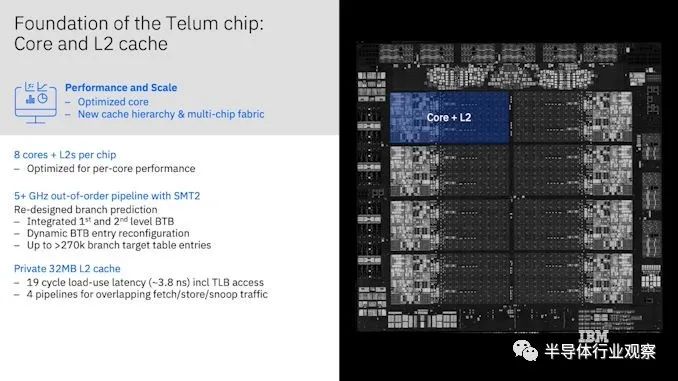

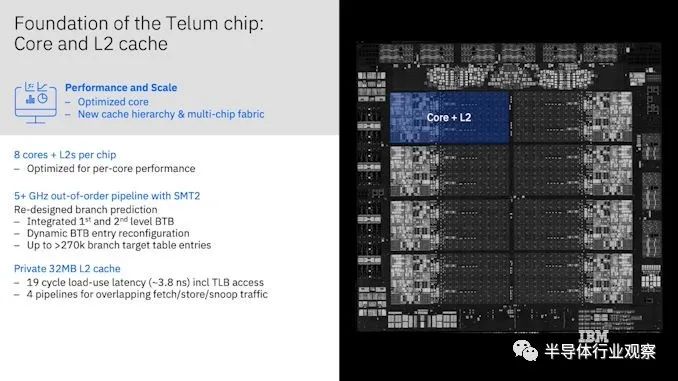

在单个芯片上,我们有八个内核。每个内核具有 32 MB 的私有 L2 缓存,具有 19 个周期的访问延迟。这对于 L2 缓存来说是一个很长的延迟,但它也比 Zen 3 的 L2 缓存大 64 倍,这是一个 12 周期的延迟。

从芯片设计来看,中间的所有空间都是 L2 缓存。没有 L3 缓存。没有可供所有内核访问的物理共享 L3。如果没有 z15 那样的集中式缓存芯片,这意味着为了让具有一定数量共享数据的代码能够工作,它需要往返主内存,这很慢。但IBM已经想到了这一点。

从表面上看,每个 L2 缓存确实是每个核心的私有缓存,而32MB是非常巨大的。但是,当需要从 L2 逐出缓存行时,无论是处理器有意还是需要腾出空间,而不是简单地消失,它会尝试在芯片上的其他地方寻找空间。如果它在不同内核的 L2 中找到一个空间,它就会坐在那里,并被标记为 L3 缓存线。

IBM 在这里实施的是存在于私有物理缓存中的共享虚拟缓存的概念。这意味着 L2 缓存和 L3 缓存成为相同的物理事物,并且缓存可以根据工作负载的需要包含来自所有不同内核的 L2 和 L3 缓存线的混合。这对于租户不需要完整 CPU 的云服务(是的,IBM 在其云中提供 IBM Z)或不能完全跨内核扩展的工作负载变得很重要。

这意味着具有 8 个私有 32 MB L2 缓存的整个芯片也可以被视为具有 256 MB 共享“虚拟”L3 缓存。在这种情况下,考虑消费领域的等效情况:AMD 的 Zen 3 小芯片具有 8 个内核和 32 MB 的 L3 缓存,每个内核只有 512 KB 的私有 L2 缓存。如果它实现了像 IBM 这样更大的 L2/虚拟 L3 方案,我们最终会得到每个核心 4.5 MB 的私有 L2 缓存,或者每个小芯片 36 MB 的共享虚拟 L3。

这种 IBM Z 方案有一个优势,如果一个核心恰好需要位于虚拟 L3 中的数据,而该虚拟 L3 线路恰好位于其私有 L2 中,那么 19 个周期的延迟比共享的低得多。物理 L3 缓存将是(~35-55 个周期)。然而,更有可能的是,所需的虚拟 L3 高速缓存线位于不同内核的 L2 高速缓存中,IBM 表示,在其具有 320 GB/s 带宽的双向环互连中,这会导致平均 12 纳秒的延迟。5.2 GHz 下的 12 纳秒约为 62 个周期,这将比物理 L3 缓存慢,但更大的 L2 应该意味着 L3 使用的压力更小。但也因为 L2 和 L3 的大小是如此灵活和大,根据工作负载,整体延迟应该更低,工作负载范围应该增加。

但IBM的设计优势远不止于此。我们必须更深入地探讨。

对于IBM Telum,我们在一个封装中有两个芯片,一个单元中有四个封装,一个系统中有四个单元,总共有32个芯片和256个内核。IBM 没有使用外部 L4 缓存芯片,而是更进一步,使每个私有 L2 缓存也可以容纳相当于虚拟 L4 的缓存。

这意味着如果一个缓存线从一个芯片上的虚拟 L3 中被逐出,它会去寻找系统中的另一个芯片来生存,并被标记为虚拟 L4 缓存线。

这意味着,从单核的角度来看,在一个 256 核的系统中,它可以访问:

- 32 MB 私有二级缓存(19 周期延迟)

- 256 MB 片上共享虚拟 L3 缓存(+12ns 延迟)

- 8192 MB / 8 GB 的片外共享虚拟 L4 缓存(+? 延迟)

从技术上讲,从单核的角度来看,这些数字应该是 32 MB / 224 MB / 7936 MB,因为单核不会将 L2 线驱逐到自己的 L2 中并将其标记为 L3,依此类推。

IBM 表示,使用这种虚拟缓存系统,每个内核的缓存相当于 IBM z15 的 1.5 倍,而且还改善了数据访问的平均延迟。总体而言,IBM 声称每个插槽的性能提高了 40% 以上。其他基准目前不可用。

在我看来,这就是魔法。当我第一次看到这个时,我对实际发生的事情感到有点惊讶。

在会后的问答环节中,Christian Jacobi 博士(Z 的首席架构师)表示,该系统旨在跟踪缓存未命中的数据,使用广播,并跟踪内存状态位以向外部芯片广播。这些贯穿整个系统,当数据到达时,它确保它可以被使用,并在处理数据之前确认所有其他副本都已失效。在作为活动的一部分的 slack 频道中,他还表示正在进行大量的循环计数!

说实话,像这样的事情有很多工作要做,而且可能仍然有很多考虑要向 IBM 提出关于其操作的考虑,例如有功功率,或者缓存是否在空闲状态下断电,甚至被排除在接受之外完全驱逐以保证单个内核的性能一致性。它让我思考在 x86 领域,甚至消费设备中什么是相关的和可能的。

如果我不提及 AMD 即将推出的 V-cache 技术,那么我们的讨论是不完整的。该技术通过在顶部添加垂直堆叠的 64 MB L3 小芯片,设置为每个小芯片启用 96 MB 的 L3 缓存,而不是 32 MB。但是,如果该小芯片不是 L3,而是考虑每个内核额外 8 MB 的 L2,并且能够接受虚拟 L3 缓存线,这对性能意味着什么?

最终,我与一些行业同行讨论了 IBM 的虚拟缓存理念,他们的评论从“它不应该很好地工作”到“它很复杂”以及“如果他们能像所说的那样做,那就太酷了”。

![]()

![]()