半导体技术已经发展到没有人可以假设芯片将永远存在的地步。如果不仔细考虑,老化会缩短 IC 的寿命,使其低于预期应用的需求。

老龄化在技术界得到了很好的研究,但是虽然其他不太直接参与的人可能在一般层面上理解这是一个问题,但原因并不总是很明显。那么衰老背后的物理机制究竟是什么?

“老化基本上取决于我们通过晶体管通道驱动电子的速度,”西门子 EDA的 AMS 产品管理负责人 Sathish Balasubramanian 说。

这反过来又会带来一些权衡。“从设计的角度来看,几乎每个设计师都对老化方面的不同事物感兴趣,”自适应系统部门 Fraunhofer IIS Engineering 的质量和可靠性小组经理 André Lange 说。

也就是说,它的形象已经上升为一个关键的验证目标。“我们一直专注于 PPA,”Balasubramanian 说。“应该是 PPA 2 ”,考虑到四个关键因素——性能、功率、面积和老化。

只有少数已知会缩短芯片寿命的效应,其中许多都涉及电荷被困在不属于它们的地方。有些可以通过技术改进来缓解,而有些则需要仔细设计和验证。老化模拟已被证明对设计师有很大帮助,但没有快速简便的解决方案。最终,随着系统老化,片内监控有助于密切关注现场系统。

为什么我们现在担心老化

电路老化一直存在。然而,在过去,硅和其他材料可以做的事情有更多的余地和更少的限制。“老化效应和降解机制在理论上一直存在,”proteanTecs 产品营销高级总监 Marc Hutner 说。“我们开始看到的是它们在高性能应用程序中的广泛表现,例如数据中心。大型超大规模企业正在报告他们不习惯看到的计算故障和随机缺陷。我们预计,随着设计的缩小、技术节点的进步以及性能和可靠性要求的激增,这一趋势将会增加。”

过去,由于老化导致的设备故障可能会在芯片的预期寿命之后很久才出现——如果有的话。然而,随着节点越来越激进,材料的推动力越来越大,出错的空间也越来越小。老化可能发生得更快,如果处理不当,设备的预期寿命甚至比其预期系统的寿命更短。

虽然半导体老化会影响任何应用,但一个市场比其他任何市场都更关注它。“汽车是在设计中考虑设备老化的主要驱动力,”Fraunhofer 的 Lange 说。

这是由于两个因素——汽车的使用寿命必须比普通智能手机长得多,而且故障可能会产生安全后果。因此,原始设备制造商和一级供应商不得不仔细研究老化效应以及如何保护系统免受老化影响。

但除了汽车之外,任何必须持续很长时间的芯片都会受到影响。Balasubramanian 说:“我们正在尝试进行城市规划,例如污水控制系统、工业物联网中的关键任务或边缘系统,在这些系统中,给定芯片的每个最终应用都决定了如何加固它们以防老化。”

虽然有许多关于如何减轻衰老影响的信息来源,但对衰老根源的挖掘却很少。目前尚不清楚具有电子穿过它们的稳定材料会以何种方式磨损。事实证明,导致衰老的影响相对较少,并且大多数与移动电子遇到物体时所传递的能量有关。

金属迁移

第一个已知影响是一个古老的影响,可以追溯到几十年前。这里的问题是,当电子在导体中碰撞时,它们实际上可以推动金属离子。效果是渐进的,但随着时间的推移,导体中会出现间隙。即使没有完全断开连接,它的电阻也会随着它变窄而增加。

这种效应是由电流密度驱动的。随着空隙的形成,这会产生正反馈效应。电流密度与流过导体横截面的电流量有关。如果该导体因电迁移而变窄,则可用横截面会减少,从而增加电流密度并使问题恶化。

缓解涉及管理电流密度。可以通过增加金属横截面(通过加宽金属,因为高度是固定的)或降低电流来减少它。长期以来,仿真工具使运行检查成为可能,以确保电流密度在整个设计中保持在界限内。

还有另一种形式的金属迁移可能会或可能不会成为问题。金属-介电界面可能是物理应力的来源,这会导致金属移动。这是双镶嵌铜工艺早期的一个问题,金属壁上的应力。

这通常被认为是一个固定的问题,但尚不清楚它是否会在最具攻击性的节点上再次抬头。

被俘获电荷

的影响 导体和绝缘体的概念简单地假设电荷载流子仅在导体中移动并且绝缘体是电惰性的。虽然这可能是真的,但普遍存在的被困电荷问题违反了这一原则。

俘获电荷是一种以某种方式嵌入绝缘体中的电荷。它可能会四处移动,但最有可能留在原地。因为这些电荷不是流动的,它们不会直接参与任何电流流动,但它们会导致泄漏并最终导致击穿。

在大多数情况下,电荷俘获是一种不受欢迎的现象。虽然一些应用程序(如闪存)可以利用电荷捕获作为存储机制,但在其他方面无济于事。

陷阱可以被认为是吸引和保持电子的缺陷。这是栅极电介质中最受关注的问题,其中捕获的电荷会影响阈值电压。它们还使通道中的载流子更容易穿过门。

有在制造过程中产生的内在陷阱,也有在操作过程中产生的外在陷阱。由于后者,捕获的电荷会随着时间的推移而积累,这确实是导致大多数老化的原因。

本征陷阱可能由不完美的电介质形成以及电介质与硅之间的界面引起。在电介质中,电荷可以被捕获在绝缘体晶格中存在缺陷的任何地方。

虽然有可能生长出极高质量的氧化物,但它所花费的时间可能会使这种工艺变得不经济。“当你有良好的栅极氧化物时,你内部不会有太多的陷阱,”朗格说。“尽管如此,拥有这些良好的栅极氧化物需要付出更多的努力。”

由于涉及的温度和时间,退火可能不实用,具体取决于过程中的位置。“是否可以进行高温工艺步骤总是取决于之前的工艺步骤,”朗格指出。“一些高 K 电介质并不真正喜欢高温。”

现实仍然是电介质中总会存在一些缺陷。

界面处的陷阱 在

硅界面处,会有开放的或“悬空的”硅键。这些用氢钝化。但并不是每一个悬空的债券都可能被填满,剩下的那些将是陷阱。

此外,通道中的空洞可能会诱使氢气远离其位置,从而打开陷阱。“这主要是因为位于氧化硅界面的硅/氢键断裂,”西门子 EDA 模拟和混合信号产品工程总监 Ahmed Ramadan 说。

一般来说,疏水阀将取决于用于防止泄漏的材料和任何添加剂。从二氧化硅到氧化铪(或其他高 K 电介质)的转换并没有消除本征陷阱。

除非电子进入其中,否则这些缺陷不会引起问题。即便如此,单个被捕获的电子也不太可能被注意到。老化效应与这样一个事实有关,即一旦被捕获,电子可能难以脱离,这可能是一种累积效应。

以下是具有不同名称的电荷捕获的具体原因和影响,具体取决于它们的影响。虽然它们占主流应用程序老化的大部分原因,但某些应用程序——尤其是那些必须经受住严酷太空考验的应用程序——可能还有其他贡献。

“例如,由于 α 粒子,你会遇到单事件扰动,”Lange 指出。“由于高能离子也会导致永久性降解,因此总电离剂量也是一个问题。”

热载流子注入

电流中的载流子会有能量分布,其中一些会比其他的更有活力——或者说“热”。这些载流子可以使电子穿过相邻的绝缘体,将自己嵌入(甚至产生)陷阱中。这称为热载流子注入 (HCI)。

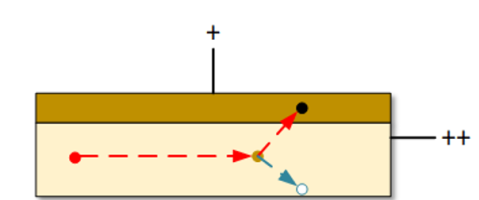

“热载流子注入是由于漏极侧发生的高电场,”Ramadan 说。“这种高电场实际上会推动获得足够能量的电子与硅晶格原子碰撞并产生电子/空穴对。孔通常会到达 NMOS 器件的衬底。电子将被推向硅/二氧化硅界面。它们将与其他硅原子碰撞,产生更多的电子/空穴对,这种效应称为“碰撞电离”。这些电子既可以驻留在二氧化硅界面内,也可以传递到栅极。”

当漏极电压相对于栅极较高时,这往往会成为更大的问题。“据说当漏极电压是栅极电压的两倍时,这是一个问题,”Ramadan 指出。

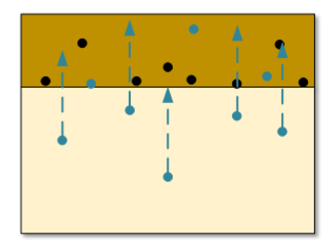

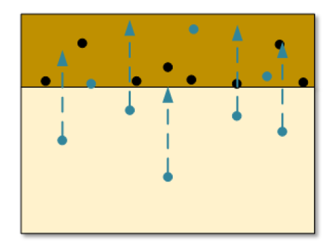

图 1:高能载流子撞击硅原子,产生电子/空穴对,电子被困在附近的电介质中。新电子可能会在此过程中产生其他电子对。孔将向基板移动。资料来源:Bryon Moyer/Semiconductor Engineering

这种机制被明确地用于闪存编程的一方面。除此之外,这是一种不受欢迎的现象。

负偏压和正偏压温度不稳定性

这是一种可以逐渐降低晶体管阈值电压的效应。负偏压温度不稳定性(NBTI) 会影响 PMOS 晶体管,并且随着时间的推移越来越受到关注。正极版本 (PBTI) 会影响 NMOS 晶体管,并且它也被考虑用于激进节点。两者都在较高温度下加剧。

对于 NBTI,捕获载波的陷阱可能有两个原因。一种是栅极电介质内存在简单的本征陷阱。这也是 PBTI 背后的主要机制。

NBTI 的另一个俘获电子来源是通道/氧化物界面。与涉及热电子的 HCI 不同,这些现象会导致电子在电场的影响下缓慢漂移进入并通过栅极电介质。请注意,这方面不被认为是影响 PBTI 的机制。

这些电子改变了晶体管的阈值。“阈值电压会下降,这会影响电路的整体延迟,这将变得更糟,”Ramadan 说。

图 2:从硅漂移到电介质中的载流子(蓝色圆圈)。黑色圆圈是陷阱,其中一些被占领。资料来源:Bryon Moyer/Semiconductor Engineering

如果去除氧化物两端的电压,体陷阱捕获的电荷会随着时间逐渐释放。“如果制造过程中存在预先存在的陷阱,它们将被孔洞填满,”Ramadan 说。“当你消除[电压]压力时,它就会消失。”

从理论上讲,PBTI 和部分 NBTI 可能是可逆的——这使得它们不是真正的老化问题。

但是解除电荷俘获的弛豫时间可以从毫秒到几小时不等。就工作集成电路的时间尺度而言,这些时间尺度很长。这意味着,即使这种效应在技术上是可逆的,但在某些电路中可能没有机会这样做。在这种情况下,它还可以有效地起到老化机制的作用。

目前尚不清楚界面陷阱是否会释放它们的电荷。“与对应于硅/氢键的空穴碰撞产生的陷阱。去除氢键会留下一个悬空的硅键,”Ramadan 说。“这些都没有恢复。”

或者换句话说,即使消除了压力,氢气也不会返回现场。

“NBTI/PBTI] 和 HCI 对电路设计人员来说很重要,因为它们都会导致晶体管性能的逐渐转变,从而导致电路性能的逐渐转变,”Lange 说。

增加泄漏

电子穿过电介质的另一种机制是隧道效应,而 Fowler-Nordheim 隧道效应是一种非常特殊的机制,通过该机制,电介质上的电压会缩小隧道势垒。电压越高或氧化物越薄,电子越容易通过隧道。

图 3:说明 Fowler-Nordheim 隧穿的简化能带图。在左侧,没有施加电压,势垒太宽而无法穿过。在右侧,在施加电压的情况下,较薄的部分可以实现隧道效应。资料来源:Bryon Moyer/Semiconductor Engineering

这种效应被有意用于原始的电可擦除可编程 ROM (E 2 PROM),并且仍然用于使用浮动栅极的位单元的闪存编程机制的一侧(另一侧使用 HCI)。但是,只要有电压穿过薄势垒,就会发生隧穿,无论是否需要。

这些电子可能会被沿途的缺陷捕获,这意味着它们可能无法穿过电介质。但它们确实降低了进一步隧穿的势垒,这可能导致通过电介质的漏电流增加。

与时间相关的电介质击穿

随着更多被俘获的电子在电介质中积累,其整体击穿电压会下降。虽然电荷缓慢积累,但在某些时候会形成“渗透路径”,从而使电介质失效。这会导致“时间相关的介电击穿”或 TDDB。

与典型的老化机制不同,这意味着会出现突然故障,而不是性能逐渐降低导致故障。虽然已经对这种效果进行了建模,但对于某些设计来说,这些模型可能过于保守。

“我们有从事 RF 工作的合作伙伴告诉我们,静态 TDDB 模型会预测电路在开启后会立即出现故障,”Lange 说。“实验表明情况并非如此。问题是您的高压尖峰非常快,以至于它们不会导致您期望从该高度的直流应力中产生的损坏。”

模型没有很好地捕捉到这一点,因此如果当今射频设计受到过度约束,则需要做更多的工作。

温度循环疲劳

先进封装带来了其自身的挑战,与可能封装在其中的单个裸片无关。“在讨论退化和老化源时,我们需要考虑的另一个因素是先进的异质封装,”Hutner 说。“这意味着我们实际上正在扩展‘老化’这个术语,以包括新现象。”

对于复杂的多芯片封装,有多种材料具有不同的热膨胀系数 (CTE)。这意味着随着温度的变化,材料将以不同的速度膨胀和收缩。随着时间的推移,这些差异可能会导致金属连接失效时的不连续性。

如果设计中没有充分解决这种长期温度循环问题,那么带有机械元件的设备(如 MEMS 芯片)也可能出现内部故障。这样的故障将导致精度下降或设备彻底死亡。

设计前分析和设计后监控

虽然了解底层机制有助于减轻芯片的老化效应,但应通过分析工具抽象出细节。这些工具的质量将取决于它们使用的模型的质量。

“如果设计人员想将他们的设计推向极限,他们需要确保他们拥有能够捕捉这些可靠性影响的良好模型,”Ramadan 指出。“大多数代工厂实际上都热衷于在他们的模型中加入 NBTI 和热载流子注入。我们还看到了专门用于汽车应用的 TDDB 模型。”

但验证老化并不像按下按钮那么简单。“这些模拟取决于您使用的任务配置文件,”Lange 警告说。“电路的用途是什么?什么是关键或典型的使用条件?另一个问题是,使用哪些模型来模拟器件退化或电路性能的影响?这些模型必须支持仿真中的其他瞬态波形。他们必须准确评估您感兴趣的 IV 曲线中的所有点。”

随着对衰老的了解越来越多,应该更新这些模型,从而更容易围绕衰老进行设计——即使每一代人的影响都会变得更糟。

“对物理上发生的事情的基本了解已经相当不错了,即使对于非常非常小的节点也是如此,”Lange 说。“但要使这些模型可用于不同的技术或不同的晶体管类型,还有很多工作要做。”

硅前验证虽然很关键,但还不够。老化是监控电路被包含在高级 IC 中的主要原因之一。“SoC 需要变得智能,嵌入智能监控解决方案,以提供有关其健康状况和性能下降预测的实时反馈,”Hutner 说。

可以观察关键参数,分析指向可能因老化而出现故障的设备。在适当的情况下,这些芯片——或者它们被焊接到的电路板——可以在它们的故障导致更大的问题之前被更换。

那么,老化效应似乎会持续存在。但是,在减缓老化的设计验证和观察老化过程的实时监控之间,系统可以得到更好的保护,因为它们越来越多地渗透到我们的生活中。

![]()