随着应用市场对于芯片性能的不断追求,芯片制造的成本也在持续增加,创新的先进封装技术的出现也成为必然。对于传统封装方式的创新,促成了晶圆级封装技术(Wafer Level Package,WLP)的“应运而生”。

晶圆级封装技术可定义为:直接在晶圆上进行大部分或全部的封装、测试程序,然后再进行安装焊球并切割,从而产出一颗颗的IC成品单元。也就是说,通过直接在晶圆上制作再布线层,然后进行植球、对晶圆减薄处理之后,晶圆才被切割成为单独的芯片单元。

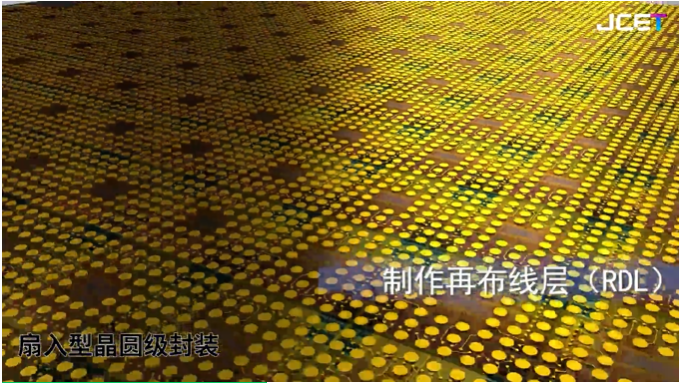

什么是扇入型晶圆级(Fan-In Wafer Level Packaging)封装?

从晶圆代工厂(Foundry)生产完成的晶圆(Wafer)经过测试后进入生产线

为了将晶圆上的接口(I/O)引出至方便焊接的位置,在晶圆上通过金属布线工艺制作再布线层(RDL)

为使芯片成品更轻薄

对晶圆进行减薄加工

再在布线层(RDL)所连接的金属焊盘上

进行植球,方便后续芯片

在印刷电路板(PCB)上的焊接

最后将晶圆进行切割

以得到独立的芯片

芯片产品通过最终测试后

即可出厂成为芯片成品

半导体成品制造业在飞速发展,长电科技将继续推进晶圆级封装技术革新,研发新的技术,优化工业流程为市场提供更高质量的芯片,推动中国半导体产业不断前行。

![]()